TMP92CZ26A

92CZ26A-499

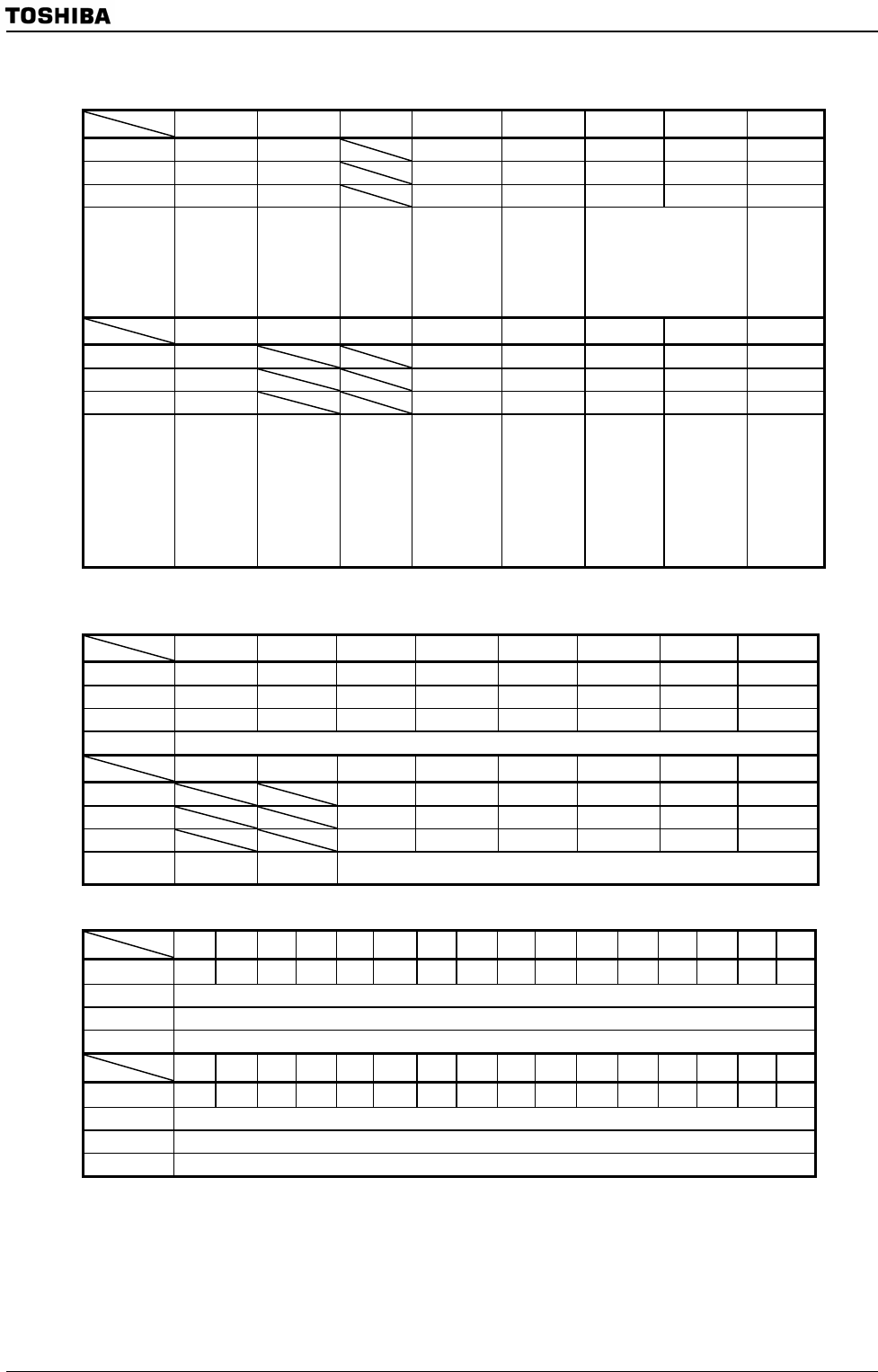

I2S1 Control Register

7 6 5 4 3 2 1 0

bit Symbol

TXE1 *CNTE1 DIR1 BIT1 DTFMT11 DTFMT10 SYSCKE1

Read/Write

R/W R/W R/W R/W R/W R/W R/W

After reset

0 0 0 0 0 0 0

Function

Transmission

0: Stop

1: Start

Counter

control

0: Clear

1: Start

Transmission

start bit

0: MSB

1: LSB

Bit length

0: 8 bits

1:16 bits

Output format

00: I

2

S 10: Right

01: Left 11: Reserved

System

clock

0: Disable

1: Enable

15 14 13 12 11 10 9 8

bit Symbol

CLKS1 FSEL1 TEMP1 WLVL1 EDGE1 CLKE1

Read/Write

R/W R/W R R/W R/W R/W

After reset

0 0 1 0 0 0

Function

Source

clock

0: f

SYS

1: f

PLL

Stereo

/monaural

0: Stereo

1: Monaural

Transmission

FIFO state

0: Data

1: No data

WS level

0: Low left

1: High left

Data output

clock edge

0: Falling

1: Rising

Clock

operation

(after

transmis-

sion)

0: Enable

1: Disable

I2S1 Divider Value Setting Register

7 6 5 4 3 2 1 0

bit Symbol CK17 CK16 CK15 CK14 CK13 CK12 CK11 CK10

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

After reset 0 0 0 0 0 0 0 0

Function Divider value for CK signal (8-bit counter)

15 14 13 12 11 10 9 8

Bit symbol WS15 WS14 WS13 WS12 WS11 WS10

Read/Write R/W R/W R/W R/W R/W R/W

After reset 0 0 0 0 0 0

Function

Divider value for WS signal (6-bit counter)

I2S1 Buffer Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

bit Symbol

B115 B114 B113 B112 B111 B110 B109 B108 B107 B106 B105 B104 B103 B102 B101 B100

Read/Write W

After reset Undefined

Function Transmission buffer register (FIFO)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

bit Symbol

B131 B130 B129 B128 B127 B126 B125 B124 B123 B122 B121 B120 B119 B118 B117 B116

Read/Write W

After reset Undefined

Function Transmission buffer register (FIFO)

Figure 3.18.3 I

2

S Channel 1 Control Registers

I2S1CTL

(1818H)

I2S1C

(181AH)

I2S1BUF

(1810H)

Read-modify-

write

instructions

cannot be

used.

(1819H)

(181BH)