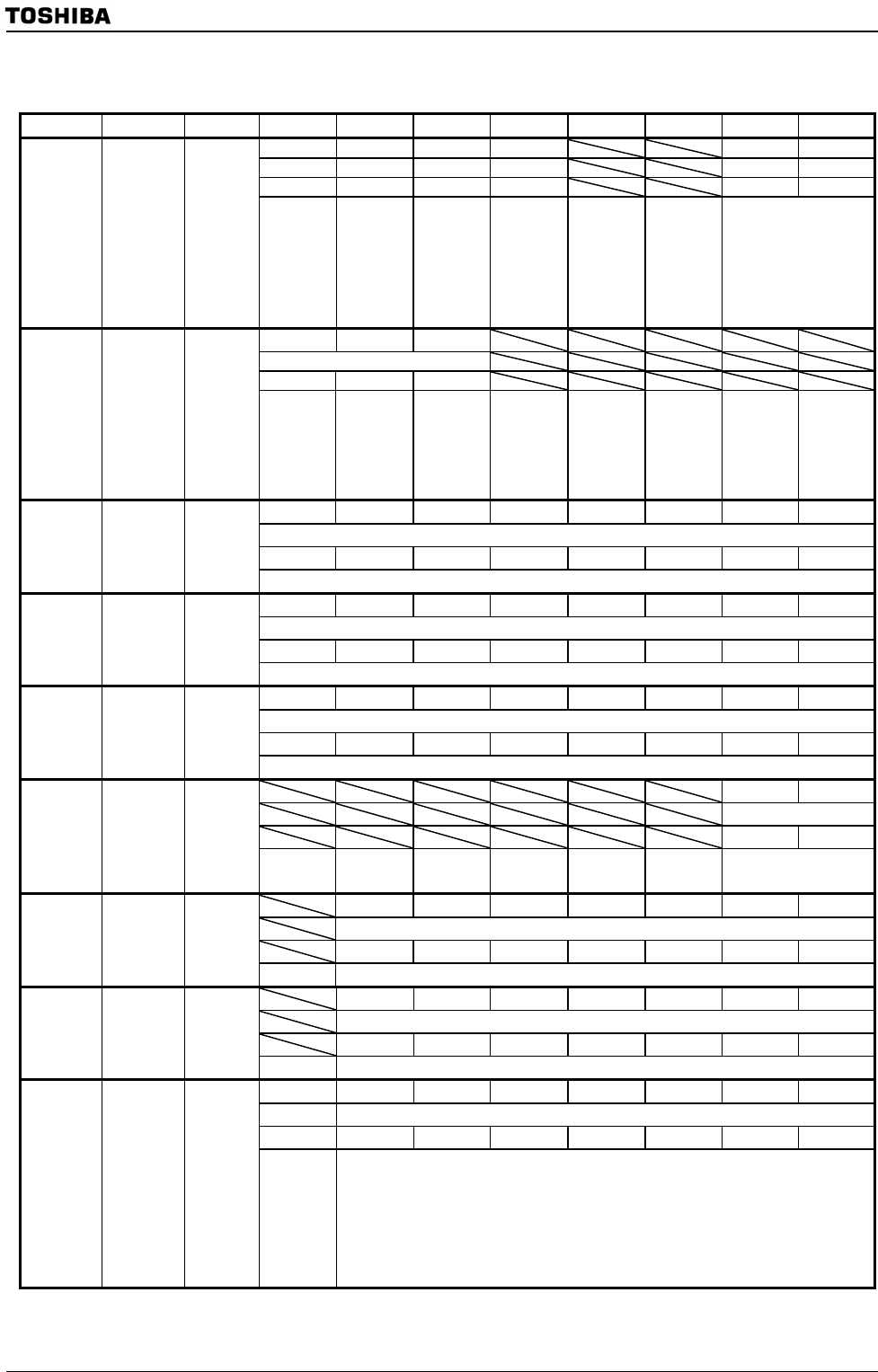

TMP92CZ26A

92CZ26A-700

(6) LCD controller (2/6)

Symbol Name

Address 7 6 5 4 3 2 1 0

LCP0P LHSP LVSP LLDP LVSW1 LVSW0

R/W R/W R/W R/W R/W R/W

1 0 1 0 0 0

LCDCTL1

LCD

control1

register

0286H

LCP0

phase

0:Rising

1:Falling

LHSYNC

phase

0:Rising

1: Falling

LVSYNC

phase

0:Rising

1: Falling

LLOAD

phase

0:Rising

1: Falling

LVSYNC

enable time control

00: 1 clock of LHSYNC

01: 2 clocks of LHSYNC

10: 3 clocks of LHSYNC

11: Reserved

LGOE2P LGOE1P LGOE0P

R/W

0 0 0

LCDCTL2

LCD

control2

register

0287H

LGOE2

phase

0: Rising

1: Falling

LGOE1

phase

0: Rising

1: Falling

LGOE0

phase

0: Rising

1: Falling

LH7 LH6 LH5 LH4 LH3 LH2 LH1 LH0

W

0 0 0 0 0 0 0 0

LCDHSP

LHSYNC

Pulse

register

028AH

LHSYNC period (bits 7-0)

LH15 LH14 LH13 LH12 LH11 LH10 LH9 LH8

W

0 0 0 0 0 0 0 0

LCDHSP

LHSYNC

Pulse

register

028BH

LHSYNC period (bits 15-8)

LVP7 LVP6 LVP5 LVP4 LVP3 LVP2 LVP1 LVP0

W

0 0 0 0 0 0 0 0

LCDVSP

LVSYNC

Pulse

register

028CH

LVSYNC period (bits 7-0)

LVP9 LVP8

W

0 0

LCDVSP

LVSYNC

Pulse

register

028DH

LVSYNC period

(bits 9-8)

PLV6 PLV5 PLV4 PLV3 PLV2 PLV1 PLV0

W

0 0 0 0 0 0 0

LCDPRVSP

LVSYNC

Pre Pulse

register

028EH

Front dummy LVSYNC (bits 6-0)

HSD6 HSD5 HSD4 HSD3 HSD2 HSD1 HSD0

W

0 0 0 0 0 0 0

LCDHSDLY

LHSYNC

Delay

register

028FH

LHSYNC delay (bits 6-0)

PDT LDD6 LDD5 LDD4 LDD3 LDD2 LDD1 LDD0

R/W W

0 0 0 0 0 0 0 0

LCDLDDLY

LLOAD

Delay

register

0290H

Data output

timing

0: Sync with

LLOAD

1: 1 clock

later than

LLOAD

LLOAD delay (bits 6-0)