16/27 XM-7002B Rev.1.0

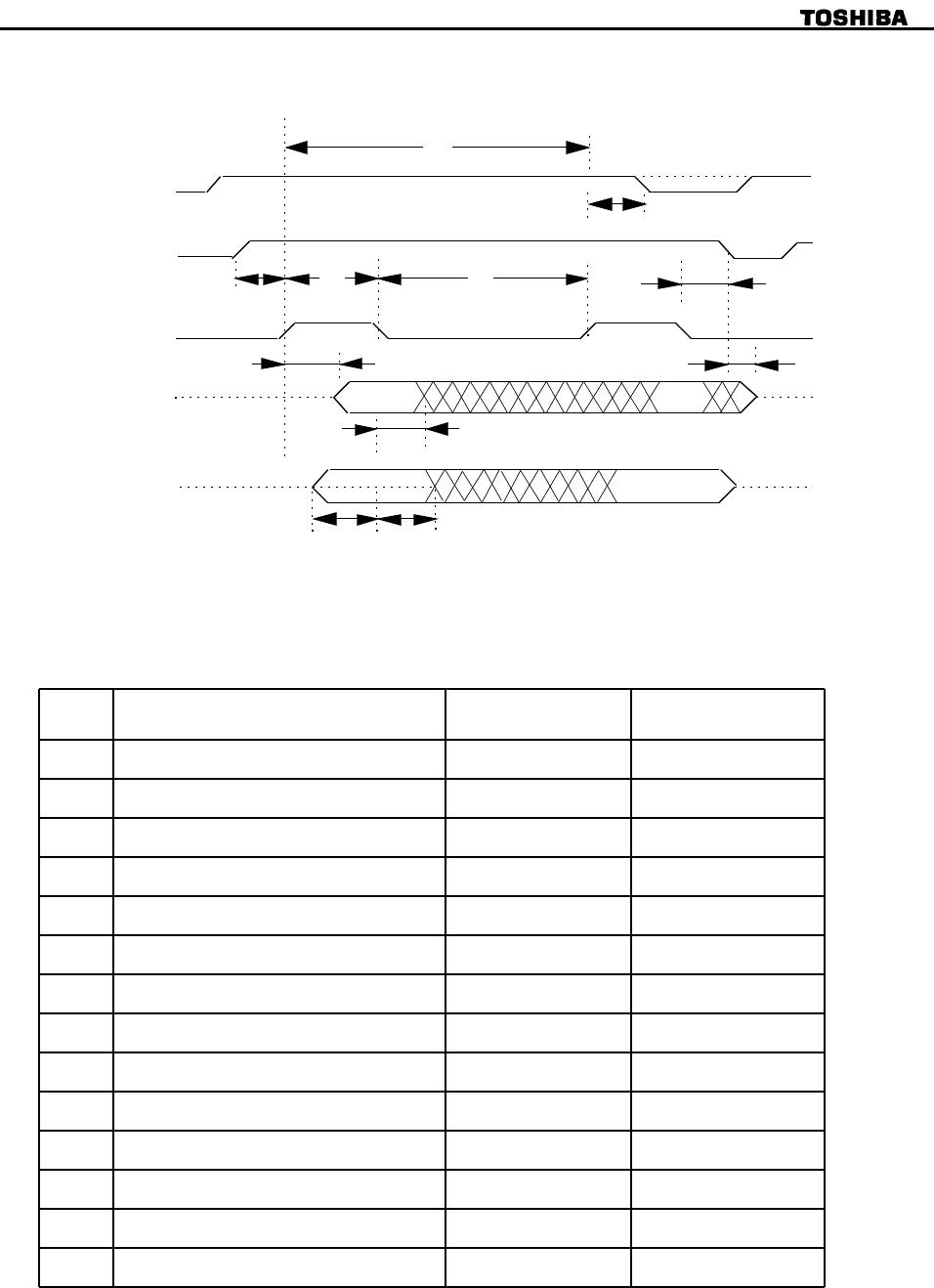

6.2.3.Timing of Host Interface (DMA Multi)

Figure 11 shows the Host Interface DMA multi word Timings

DMARQ

DMACK-*1

DIOR/DIOW-*1

Read

DD0-1

Write

DD0-1

t0

tZ

tI

tJ

tD

tE

tL

tF

tH

tG

tK

*1: In all timing diagrams, the low line indicator negated, and the upper line

indicators asserted.

Multi word DMA Mode 2

timing parameters min (ns) max (ns)

Min time (ns) Max time (ns)

t0

Cycle time

120

tC

DMACK to DMREQ delay

---

tD

DIOR-/DIOW- 16-bit

70

tE

DIOR- data access

50

tF

DIOR- data hold

5

tZ

DMACK- to tristate

25

tG

DIOR/DIOW- data setup

20

tH

DIOW- data hold

10

tI

DMACK to DIOR-/DIOW- setup

0

tJ

DIOR-/DIOW- to DMACK hold

5

tKr

DIOR- negated pulse width

25

tKw

DIOW- negated pulse width

25

tLr

DIOR- to DMREQ delay

35

tLw

DIOR- to DMREQ delay

35

Figure 11 Host Interface Timing (DMA Multi)