T

T

T

S

S

S

8

8

8

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

S

S

S

-

-

-

S

S

S

T

T

T

S

S

S

1

1

1

6

6

6

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

S

S

S

-

-

-

S

S

S

/

/

/

M

M

M

T

T

T

S

S

S

3

3

3

2

2

2

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

S

S

S

-

-

-

S

S

S

/

/

/

M

M

M

T

T

T

S

S

S

6

6

6

4

4

4

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

S

S

S

-

-

-

S

S

S

/

/

/

M

M

M

T

T

T

S

S

S

1

1

1

2

2

2

8

8

8

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

S

S

S

-

-

-

M

M

M

T

T

T

S

S

S

1

1

1

9

9

9

2

2

2

G

G

G

S

S

S

S

S

S

D

D

D

2

2

2

5

5

5

S

S

S

-

-

-

M

M

M

2.5” Solid State Disk

Transcend Information Inc.

V2.2

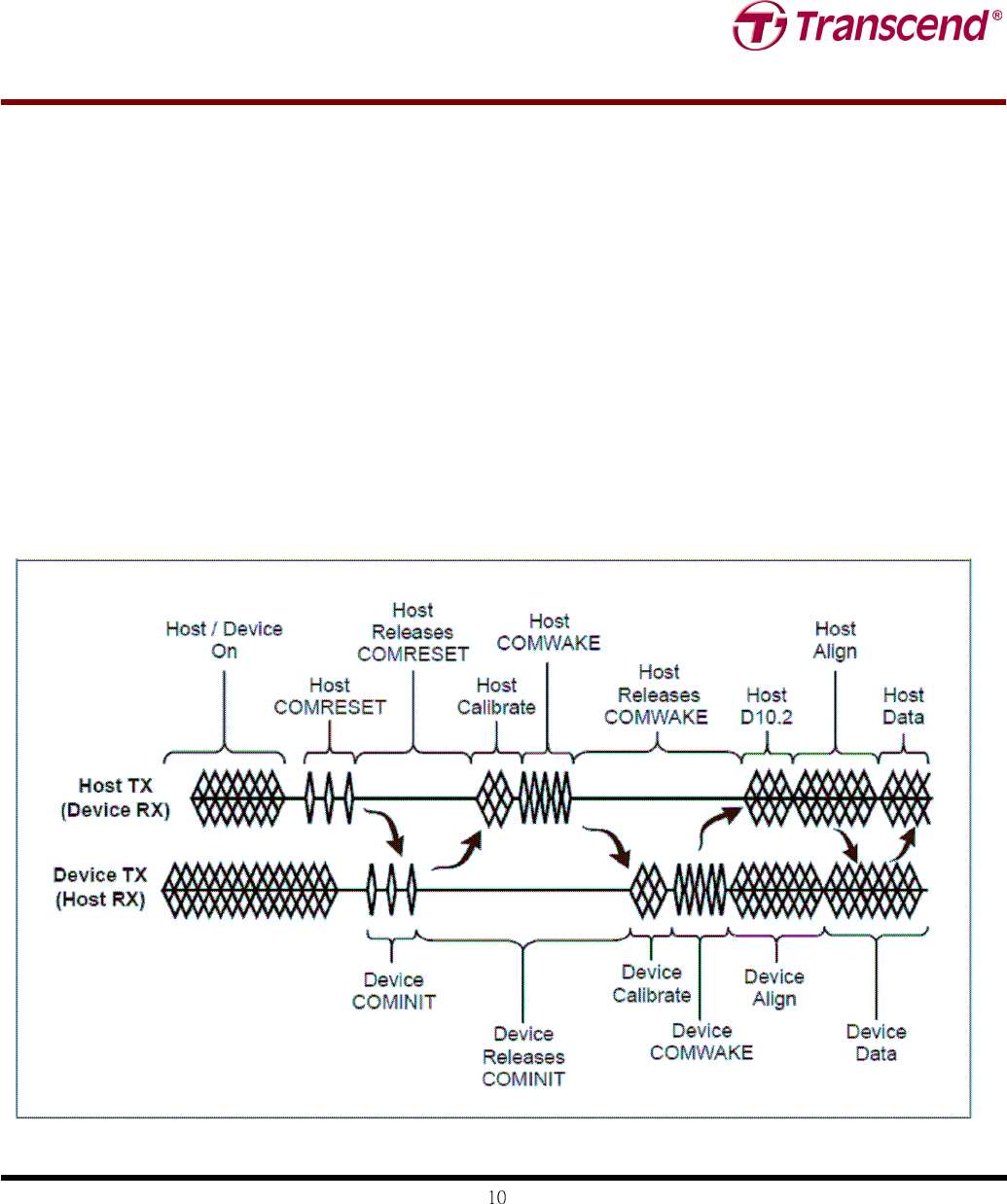

COMRESET

COMRESET always originates from the host controller, and forces a hardware reset in the device. It is indicated by

transmitting bursts of data separated by an idle bus condition. The OOB COMRESET signal shall consist of no less than six

data bursts, including inter-burst temporal spacing. The COMRESET signal shall be:

1) Sustained/continued uninterrupted as long as the system hard reset is asserted, or

2) Started during the system hardware reset and ended some time after the negation of system hardware reset, or

3) Transmitted immediately following the negation of the system hardware reset signal.

The host controller shall ignore any signal received from the device from the assertion of the hardware reset signal until the

COMRESET signal is transmitted. Each burst shall be 160 Gen1 UI’s long (106.7 ns) and each inter-burst idle state shall be

480 Gen1 UI’s long (320 ns). A COMRESET detector looksfor four consecutive bursts with 320 ns spacing (nominal). Any

spacing less than 175 ns or greater than 525 ns shall invalidate the COMRESET detector output. The COMRESET

interface signal to the Phy layer shall initiate the Reset sequence shown in Figure 5 below. The interface shall be held

inactive for at least 525 ns after the last burst to ensure far-end detector detects the negation properly.

Figure 5 : comreset sequence