84 Chapter 4

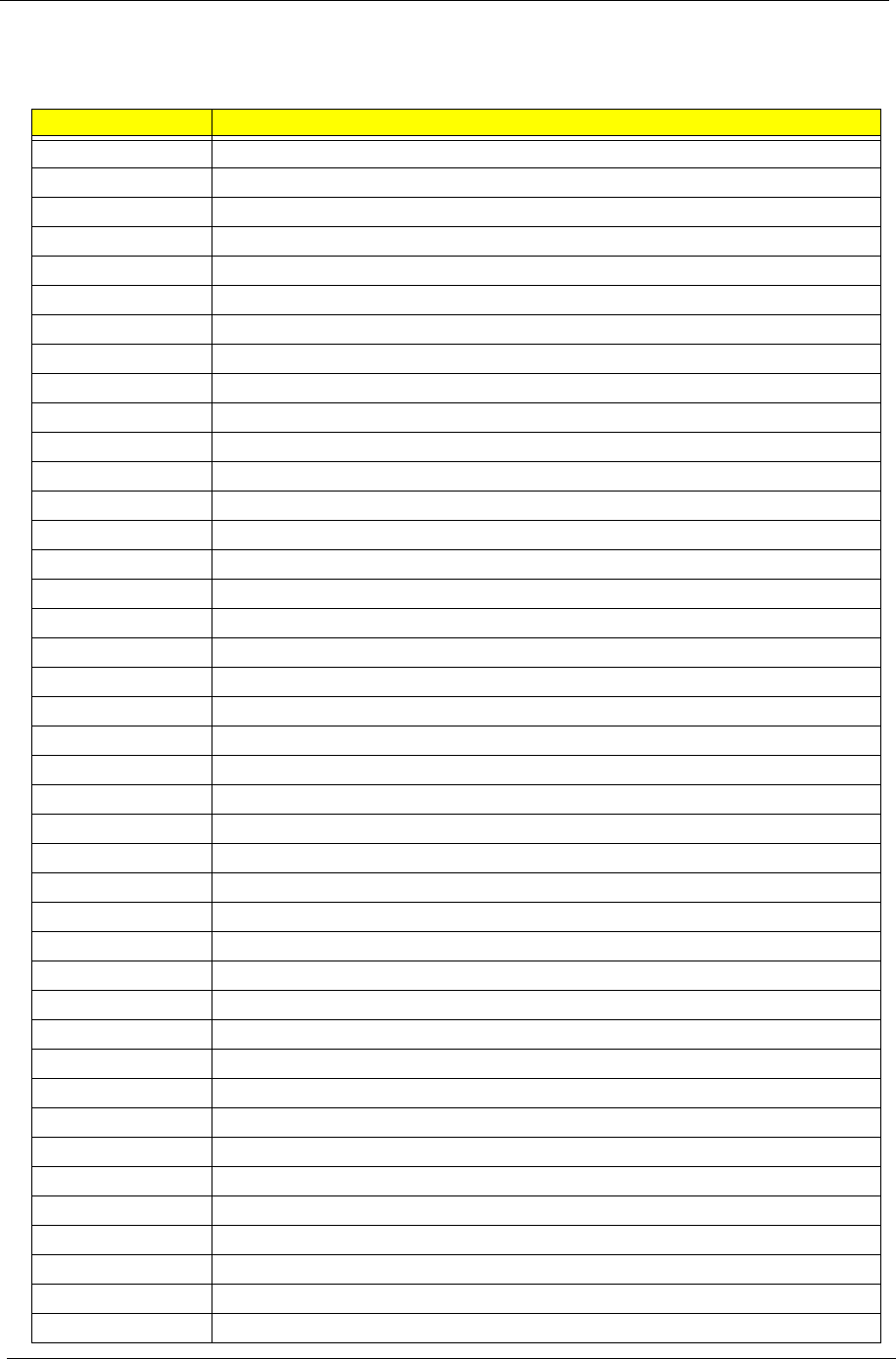

Post Code Table

POST Code Description

01 Prepare PEI Event Log service (bios debug purpose)

02 OEM service Initialization (bios debug purpose)

04 Status code report service initialization (bios debug purpose)

05 CPU IO and PCI IO (bios debug purpose)

08 CPU Initialization

09 PC Init at stage 1 (SB related init)

0A Firmware Flash Device (for BIOS ROM) Read Services (bios debug purpose)

0D PC Init at stage 2 (NB related init)

0E SMbus

10 Memory Initialization

11 Restore system configuration for S3 resume (bios debug purpose)

12 Clock generator Initialization

13 Provide TPM Presence policy (bios debug purpose)

14 TPM Module

2F Extract BIOS ROM to memory

32 Prepare services for S3 resume (bios debug purpose)

33 Prepare services for S3 resume (bios debug purpose)

34 8254 timer chip initialization

36 PCX decoder

37 CPU Initialization

38 Prepare stall (delay) related services (bios debug purpose)

39 BIOS ROM reclaims relative

3A Install EFI Runtime Protocol (bios debug purpose)

3B The counter for System boot times (bios debug purpose)

3C Watchdog timer service initialization (bios debug purpose)

3D EFI driver format verification (bios debug purpose)

3E Provide CPU IO protocol service (bios debug purpose)

3F Provide reset service (bios debug purpose)

40 Real Time Clock Initialization

41 Status code report service initialization (bios debug purpose)

42 Firmware Flash Device (for BIOS ROM) Read/Write Services

43 Firmware Flash Device Read/Write for BIOS ROM recovery (bios debug purpose)

46 PC Init at stage 1 (SB related init)

46 PCI Host Bridge Initialization

47 PCI-E Initialization

48 SB Controller Initialization

4A SATA Controller Initialization

4B SM Bus Initialization

4D NB Initialization

4D ISA Bus Initialization

4E ISA Serial Device Initialization