A

B

E

DESIGN

C

D

67

6

A

UPDATE SHEET

REV.

CUSTOMER

6/14

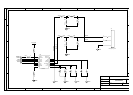

MCS LOGIC

45

12

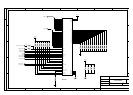

BANK0

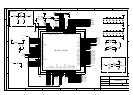

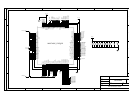

SDRAM BANK

BANK1

2003.11.18

MLN7400EN

8

9

MEMORY

3

X8

X16

FLASH

12 3

AMD Flash

BANK

Selection

BANK2

REMARK

CHECK-1

CHECK-2

BOSIZE : 8 Bit

BOSIZE : 16Bit

45

DATE

B

C

D

E

R80

0

13

14

C40 0.1uF

14

I_O6

I_O7

15

16

I_O8

I_O9

29

LB*

39

NC1

22

23

NC2

NC3

28

41

OE*

40

UB*

VCC1

11

33

VCC2

12

VSS1

VSS2

34

WE*

17

A7

20

21

A8

A9

24

CS*

6

I_O1

7

30

I_O10

I_O11

31

32

I_O12

I_O13

35

36

I_O14

I_O15

37

38

I_O16

8

I_O2

I_O3

9

10

I_O4

I_O5

13

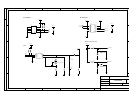

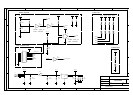

K6R1016V1D_SRAM

U6

1

A0

A1

2

25

A10

A11

26

27

A12

A13

42

43

A14

44

A15

3

A2

A3

4

5

A4

A5

18

19

A6

VCC_33

4

5

5

15

6

7

9

10

11 13

14

0

1

2

3

GROUND

3

4

9

8

11

12

10

10

9

10

1

2

16

17

6

7

C35 0.1uF

0.1uFC36

12

14

15

GROUND

7

20

0

R77

14

14

0

15

C39 0.1uF

R74

0

7

8

13

24

OE*

32

VDD

WE*

31

0.1uFC41

C42 0.1uF

0

R73

A4

8

7

A5

A6

6

5

A7

A8

27

26

A9

22

CE*

13

DQ0

DQ1

14

15

DQ2

DQ3

17

18

DQ4

19

DQ5

DQ6

20

DQ7

21

16

GND

U9

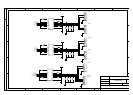

AT29C040A

A0

12

11

A1

A10

23

25

A11

A12

4

28

A13

A14

29

A15

3

2

A16

30

A17

A18

1

A2

10

9

A3

C44 0.1uF

2

3

12

6

VCC_33

0

11

12

15

7

8

0.1uFC43

46

VSS1

VSS2

27

10

11

7

8

VCC_33

0

GROUND

D11

36

39

D12

D13

41

43

D14

D15

45

33

D2

D3

35

38

D4

D5

40

42

D6

D7

44

30

D8

D9

32

15

RY_BY#

37

VCC

13

VPP

17

A17

A18

16

A19

9

A2

23

10

A20

22

A3

A4

21

20

A5

A6

19

18

A7

A8

8

7

A9

BYTE_VCCQ

47

29

D0

D1

31

34

D10

AM29LV160BB

*CE

26

*OE

28

*RST

12

11

*WE

14

*WP

A0

25

24

A1

A10

6

5

A11

A12

4

3

A13

A14

2

A15

1

48

A16

5

6

VCC_33

1

2

10uF_16V

TC6

21

U8

13

12

13

4

5

6

14

15

6

11

12

12

13

18

4

0.1uFC38

0.1uFC45

C46 0.1uF

4.7K

R76

3

4

10

11

3

13

14

8

9

16

17

1

2

1

2

15

GROUND

0.1uFC32

VDD1

1

14

VDD2

VDD3

27

3

VDDQ1

VDDQ2

9

43

VDDQ3

VDDQ4

49

28

VSS1

VSS2

41

54

VSS3

VSSQ1

6

12

VSSQ2

VSSQ3

46

52

VSSQ4

16

WE*

DQ12

48

50

DQ13

DQ14

51

53

DQ15

DQ2

5

7

DQ3

DQ4

8

10

DQ5

DQ6

11

13

DQ7

DQ8

42

44

DQ9

DQMH

39

15

DQML

NC

40

RAS*

18

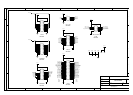

A2

25

26

A3

A4

29

30

A5

A6

31

32

A7

A8

33

34

A9

CAS*

17

37

CKE

CLK

38

19

CS*

DQ0

2

4

DQ1

DQ10

45

47

DQ11

3

3

VCC_33

U7

4MX16_SDRAM

A0

23

24

A1

A10

22

35

A11

A12

36

20

A13

A14

21

7

19

2

6

1K

R79

9

10

R75

4.7K

4

VCC_33

GROUND

GROUND

0

SW2

SW_DPDT

1

2

3

4

5

5

6

C33 0.1uF

3

9

0

1

18

4

5

R72

0

0.1uFC34

VCC_33

C37 0.1uF

8

0

1

2

6

7

VCC_33

GROUND

GROUND

0

1

4

5

VCC_33

11

5

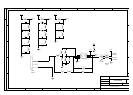

ADDR(20:0)

NCS_AMD

NEOE

NEWE

NRESET

NECS2

NECS0

ADDR(20)

NCS_AMDDATA(15:0)

NEOE

NEWE

R78

4.7K

ADDR(15:0) DATA(15:0)

NECS1

NBE0_LB

NBE1_UB

ADDR(18:0)

NECS0

NEOE

NEWE

DATA(15:0)

ADDR(14:0)

SDCLK

SDCKE

SDCSN

SDRASN

SDCASN

SDWEN

ADDR(15)

ADDR(16)

DATA(15:0)