51

APPENDIX

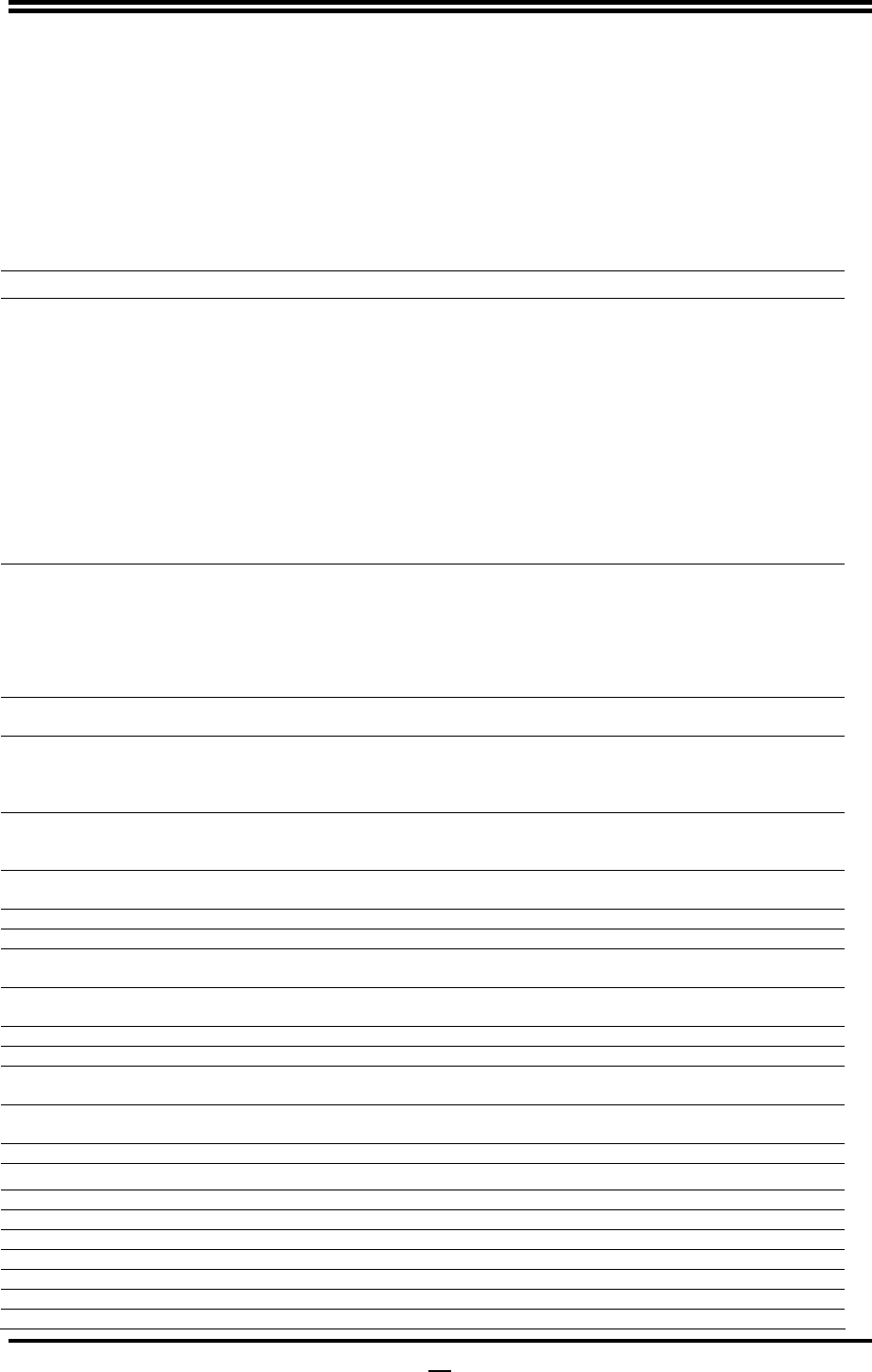

Debug Port Post Code

Normal POST Codes

NOTE: EISA POST codes are typically output to port address 300h.

ISA POST codes are output to port address 80h.

Code(hex) Name Description

C0 Turn Off Chipset

And CPU test

OEM Specific-Cache control cache

Processor Status (1FLAGS) Verification.

Tests the following processor status

flags: Carry, zero, sign, overflow,

The BIOS sets each flag, verifies

They are set, then turns each flag

off and verifies it is off.

Read/Write/Verify all CPU registers

except SS, SP, and BP with data

pattern FF and 00.

RAM must be periodically refreshed to

keep the memory from decaying. This

function ensures that the memory

refresh function is working properly.

C1 Memory Presence First block memory detect

OEM Specific-Test to size on-board

memory. Early chip set initialization

Memory presence test

OEM chip set routines

Clear low 64K of memory

Test first 64K memory.

C2 Early Memory

Initialization

OEM Specific- Board Initialization

C3 Extend Memory DRAM

select

OEM Specific- Turn on extended memory

Initialization

Cyrix CPU initialization

Cache initialization

C4 Special Display

Handling

OEM Specific- Display/Video Switch

Handling so that Switch Handling display

switch errors never occurs

C5 Early Shadow OEM specific- Early shadow enable for

fast boot

C6 Cache presence test External cache size detection

CF CMOS Check CMOS checkup

B0 Spurious If interrupt occurs in protected

mode.

B1 Unclaimed NMI If unmasked NMI occurs, display

Press F1 to disable NMI, F2 reboot.

BF Program Chip Set To program chipset from defaults values

E1-EF Setup Pages E1- Page 1, E2 - Page 2, etc.

1 Force load Default

to chipset

Chipset defaults program

2 Reserved

3 Early Superio Init Early Initialized the super IO

Code(hex) Name Description

4 Reserved

5 Blank video Reset Video controller

6 Reserved

7 Init KBC Keyboard controller init

8 KB test Test the Keyboard

9 Reserved

A Mouse Init Initialized the mouse