Chapter 3 Processor/Memory Subsystem

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition - September 1997

3-8

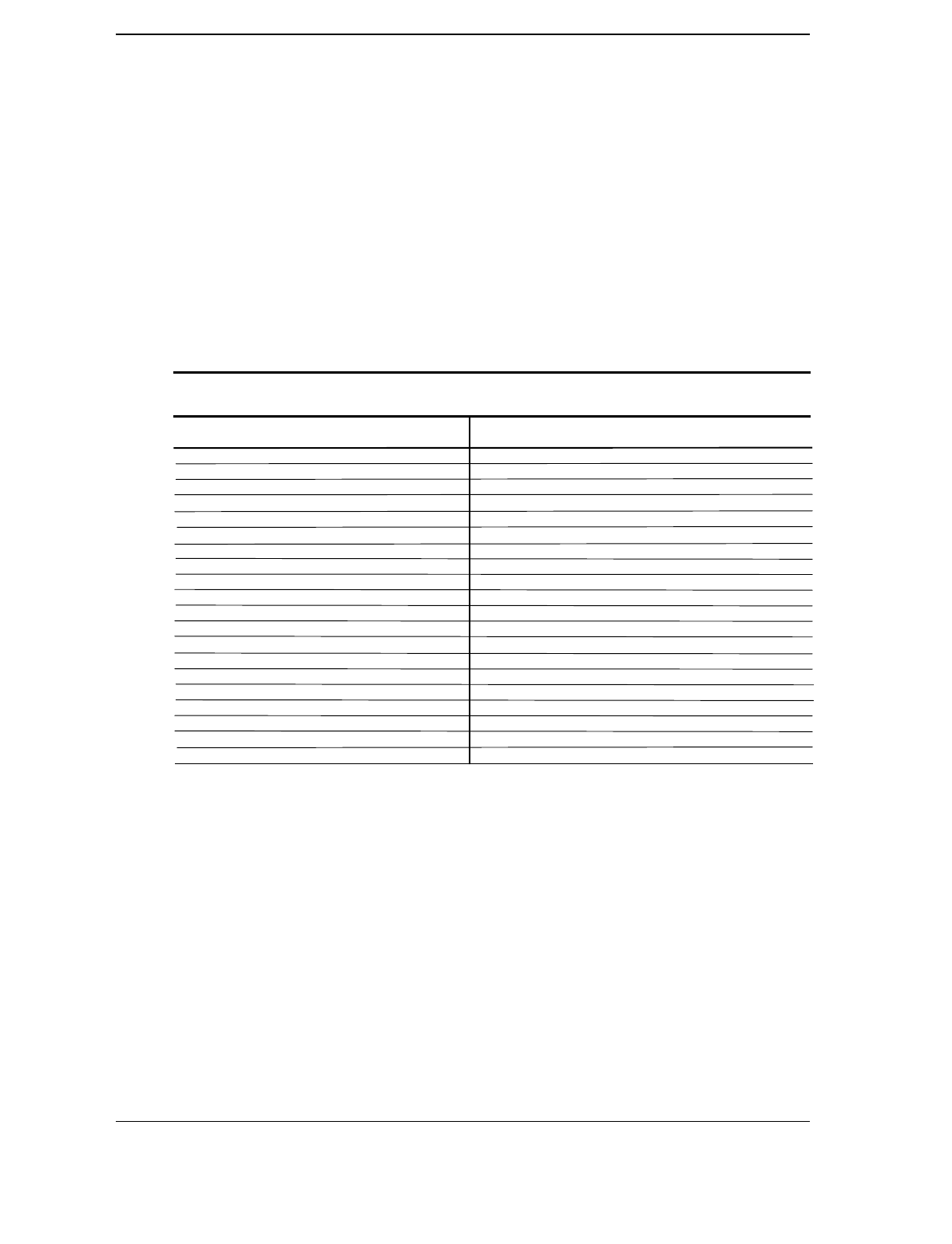

3.2.5 SUBSYSTEM CONFIGURATION

The VT82C595 component provides the configuration function for the processor/memory

subsystem. Table 3-6 lists the configuration registers used for setting and checking such

parameters as cache (L2) control, system memory control, and PCI bus operation. These registers

reside in the PCI Configuration Space and accessed using the methods described in Chapter 4,

section 4.2.

Table 3–6.

Host/PCI Bridge Configuration Registers (VT82C595)

Table 3-6.

Host/PCI Bridge Configuration Registers (VT82C595)

PCI Config.

Addr. Register

Reset

Value

PCI Config.

Addr. Register

Reset

Value

00, 01h Vender ID 1106h 64h DRAM Timing ABh

02, 03h Device ID 0595h 65h DRAM Control Reg. 1 00h

04, 05h Command 0007h 66h DRAM Control Reg. 2 00h

06, 07h Status 67h DRAM Width 00h

08h Revision ID 68h UMA Control Reg. 1 00h

09-0Bh Class Code 69h UMA Control Reg. 2 00h

0Dh Latency Timer 00h 6Ah Refresh Control 00h

0Eh Header Type 00h 6Bh Misc. Cointrol 00h

0Fh BIST (read only) 6Ch SDRAM Control

50h Cache Control Reg. 1 00h 6Dh DRAM Control Drive Strength

51h Cache Control Reg. 2 00h 6Eh ECC Control Reg.

52h Non-Cacheable Control 02h 6Fh ECC Status Reg.

53h Misc. Control 00h 70h PCI Buffer Control 00h

54, 55h Non-Cacheable Area 1 00h 71h CPU-to-PCI Flow Cntl. Reg. 1 00h

56, 57h Non-Cacheable Area 2 00h 72h CPU-to-PCI Flow Cntl. Reg. 2 00h

58h DRAM Configuration 40h 73h PCI Master Control Reg.1 00h

59h DRAM Configuration 05h 74h PCI Master Control Reg. 2 00h

5A..5Fh DRAM ROW End Addr. 01h 75h PCI Arbitration 00h

60h DRAM Type 00h 76h Extension (PCI Arbitration) 00h

61..63h Shadow RAM Control 00h -- -- --

NOTE:

Refer to VIA Technologies, Inc. documentation for detailed description of registers.

Assume unmarked locations/gaps as reserved.