Chapter 4 System Support

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition - September 1997

4-2

4.2 PCI BUS OVERVIEW

NOTE:

This section describes the PCI bus in general and highlights bus

implementation in this particular system. For detailed information regarding PCI bus

operation, refer to the PCI Local Bus Specification Revision 2.1.

This system implements a 32-bit Peripheral Component Interconnect (PCI) bus. The PCI bus

uses a shared address/data bus design. On the first clock cycle of a PCI bus transaction the bus

carries address information. On subsequent cycles, the bus carries data. PCI transactions occur

synchronously with the Host bus at a rate of up to 33 MHz, depending on the speed of the

microprocessor used. All I/O transactions involve the PCI bus. All ISA transactions involving the

microprocessor, cache, and memory also involve the PCI bus. Memory cycles will involve the

PCI if the access is initiated by a device or subsystem other than the microprocessor.

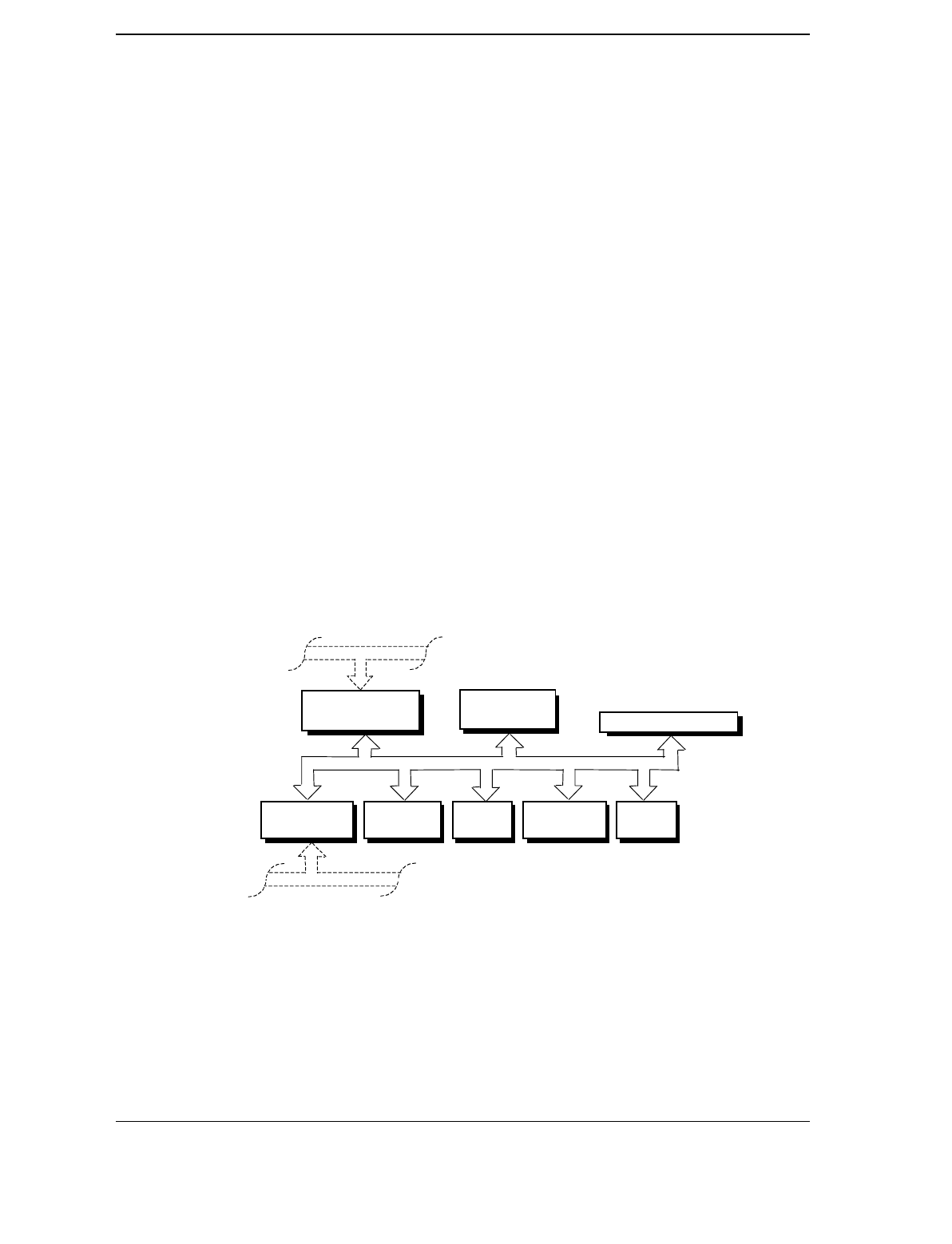

The PCI bus handles address/data transfers through the identification of devices and functions on

the bus (Figure 4-1). A device is defined as a component or slot that resides on the PCI bus. A

function is defined as the end source or target of the bus transaction. A device (component or

slot) may contain one or more functions (i.e., in this system the PCI/ISA Bridge function, EIDE

controller function, USB function, and ACPI function are contained within the South Bridge

component).

Figure 4–1.

PCI Bus Devices and Functions

32-Bit PCI Bus 0

ISA Bus

Host/PCI

Bridge Function

PCI/ISA Bridge

Function

EIDE Cntlr.

Function

PCI Connector

Host Bus

Graphics

Controller

NIC

Function

USB

Function

ACPI Cntlr.

Function