CY7C68000A

Document #: 38-08052 Rev. *G Page 13 of 15

PCB Layout Recommendations

Follow these recommendations to ensure reliable, high-perfor-

mance operation

[3]

.

■ A four-layer impedance controlled board is required to maintain

signal quality

■ Specify impedance targets (ask your board vendor what they

can achieve)

■ To control impedance, maintain trace widths and trace spacing

to within written specifications

■ Minimize stubs to minimize reflected signals

■ Connections between the USB connector shell and signal

ground must be done near the USB connector

■ Bypass and flyback capacitors on VBus, near the connector,

are recommended

■ Keep DPLUS and DMINUS trace lengths within 2 mm of each

other in length, with preferred length of 20 to 30 mm

■ Maintain a solid ground plane under the DPLUS and DMINUS

traces. Do not split the plane under these traces

■ Do not place vias on the DPLUS or DMINUS trace routing

■ Isolate the DPLUS and DMINUS traces from all other signal

traces by no less than 10 mm

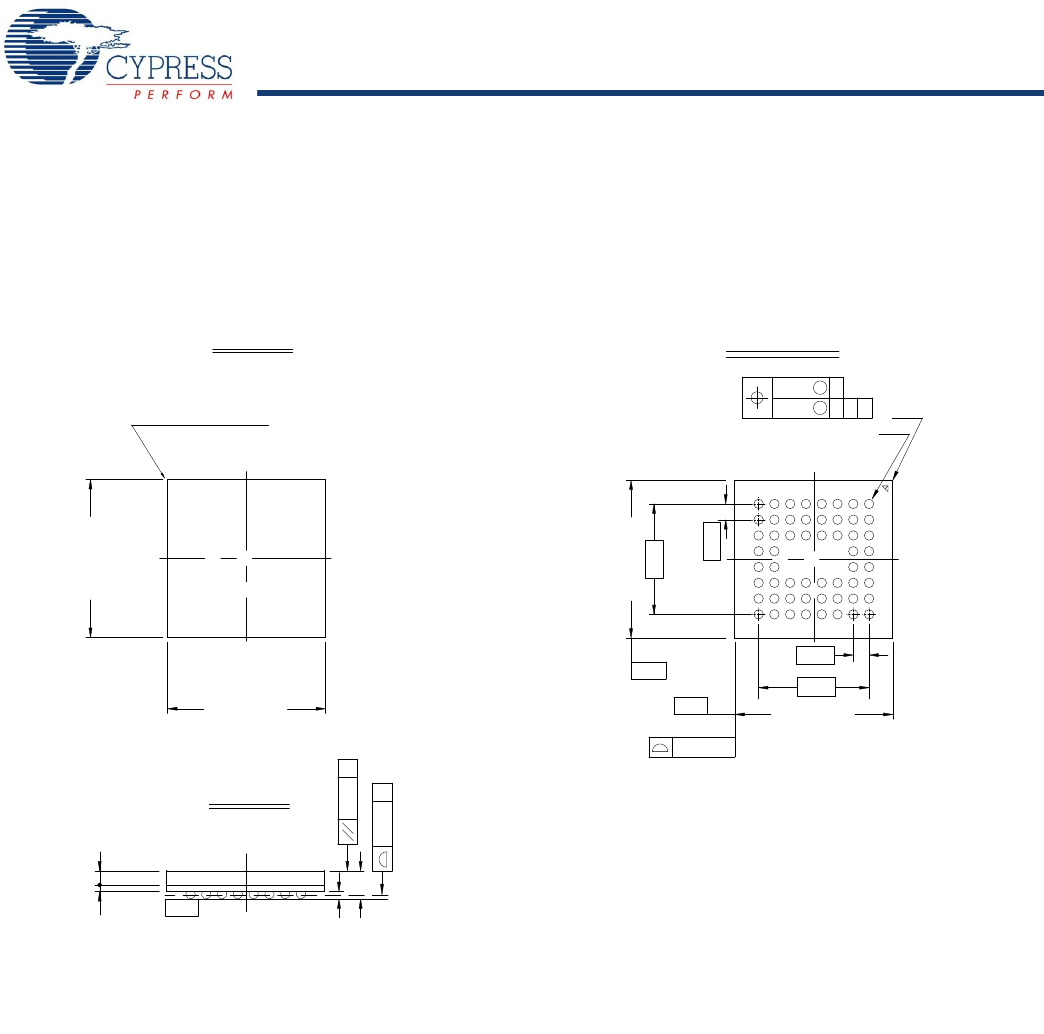

Package Diagrams (continued)

Figure 7. 56 VFBGA (5 x 5 x 1.0 mm) 0.50 Pitch, 0.30 Ball BZ56

TOPVIEW

PINA1CORNER

0.50

3.50

5.00±0.10

BOTTOMVIEW

0.10(4X)

3.50

5.00±0.10

0.50

Ø0.15MCAB

Ø0.05MC

Ø0.30±0.05(56X)

A1CORNER

-B-

-A-

1.0max

0.160~0.260

0.080C

0.45

SEATINGPLANE

0.21

0.10C

-C-

SIDEVIEW

5.00±0.10

5.00±0.10

REFERENCEJEDEC:MO-195C

PACKAGEWEIGHT:0.02 grams

E

G

H

F

D

C

B

A

13265486

7856 2341

E

G

H

F

D

C

B

A

001-03901-*B

Note

3. Source for recommendations: EZ-USB FX2™ PCB Design Recommendations, http:///www.cypress.com/cfuploads/support/app_notes/FX2_PCB.pdf

High-Speed USB Platform Design Guidelines, http://www.usb.org/developers/docs/hs_usb_pdg_r1_0.pdf.

[+] Feedback