CY7C68000A

Document #: 38-08052 Rev. *G Page 4 of 15

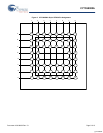

Pin Configurations

The following pages illustrate the individual pin diagrams that are available in the 56-pin QFN and 56-pin VFBGA packages.

The packages offered use either an 8-bit (60 MHz) or 16-bit (30 MHz) bus interface.

Figure 1. CY7C68000A 56-pin QFN Pin Assignment

D4

D3

V

CC

D2

Reserved

D1

D0

CLK

DataBus16_8

Uni_bidi

GND

TXValid

V

CC

ValidH

28

27

26

25

24

23

22

21

20

19

18

17

16

15

43

44

45

46

47

48

49

50

51

52

53

54

55

56

1

2

3

4

5

6

7

8

9

10

11

12

13

14

42

41

40

39

38

37

36

35

34

33

32

31

30

29

GND

D5

Reserved

D6

D7

D8

D9

Reserved

D10

D11

V

CC

D12

GND

D13

TXReady

Suspend

Reset

AV

CC

XTALOUT

XTALIN

AGND

AV

CC

DPLUS

DMINUS

AGND

XcvrSelect

TermSelect

OpMode0

V

CC

D14

D15

Reserved

Tri_state

RXError

RXActive

RXValid

GND

LineState1

LineState0

V

CC

GND

OpMode1

CY7C68000A

56-pin QFN

[+] Feedback