CY8C24223A, CY8C24423A

Document Number: 3-12029 Rev. *E Page 22 of 31

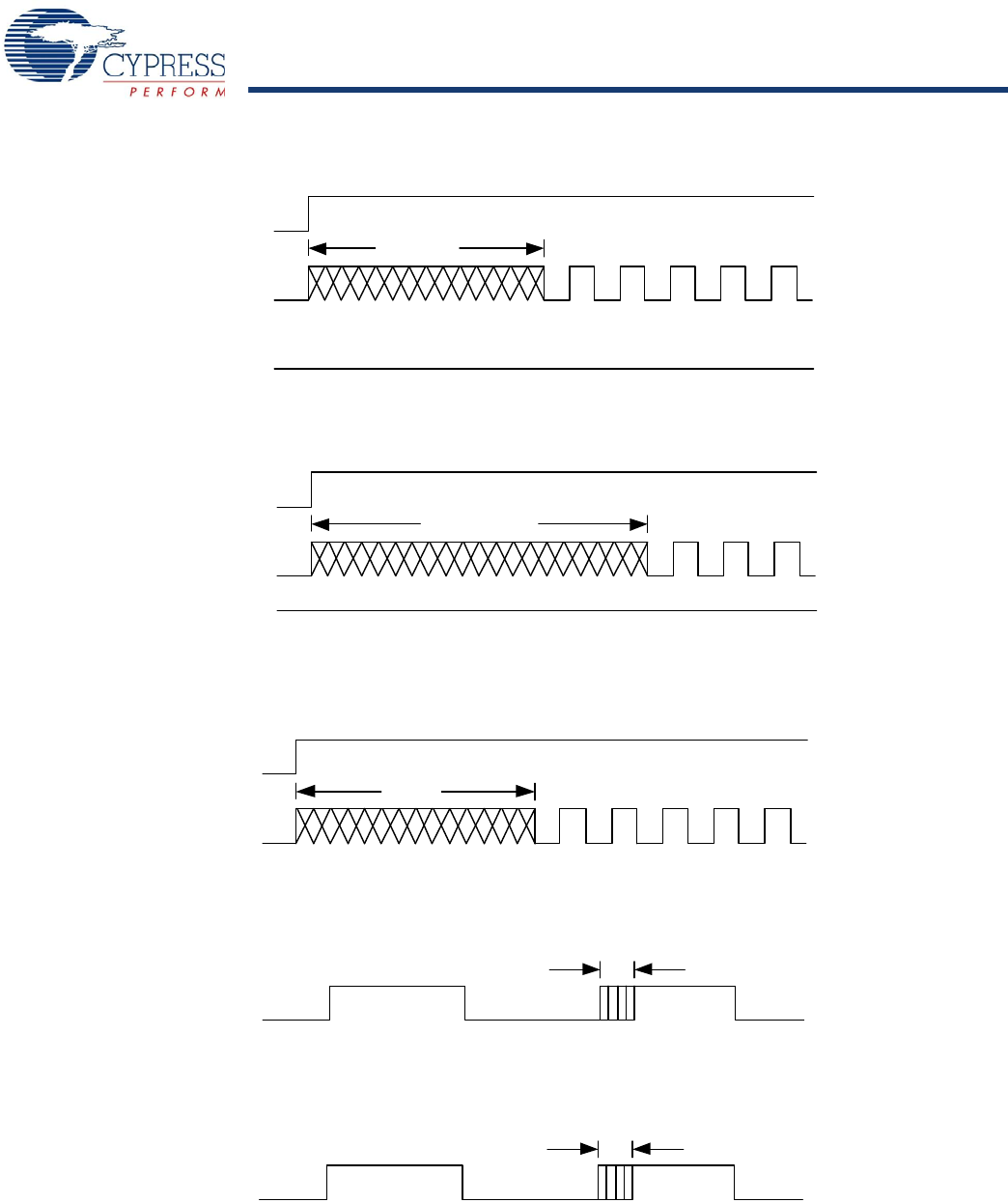

Figure 8. PLL Lock Timing Diagram

Figure 9. PLL Lock for Low Gain Setting Timing Diagram

Figure 10. External Crystal Oscillator Startup Timing Diagram

Figure 11. 24 MHz Period Jitter (IMO) Timing Diagram

Figure 12. 32 kHz Period Jitter (ECO) Timing Diagram

24 MHz

F

PLL

PLL

Enable

T

PLLSLEW

PLL

Gain

0

24 MHz

F

PLL

PLL

Enable

T

PLLSLEWLOW

PLL

Gain

1

32 kHz

F

32K2

32K

Select

T

OS

Jitter24M1

F

24M

Jitter32k

F

32K2

[+] Feedback