CYD01S36V

CYD02S36V/36VA/CYD04S36V

CYD09S36V/CYD18S36V

Document Number: 38-06076 Rev. *G Page 13 of 28

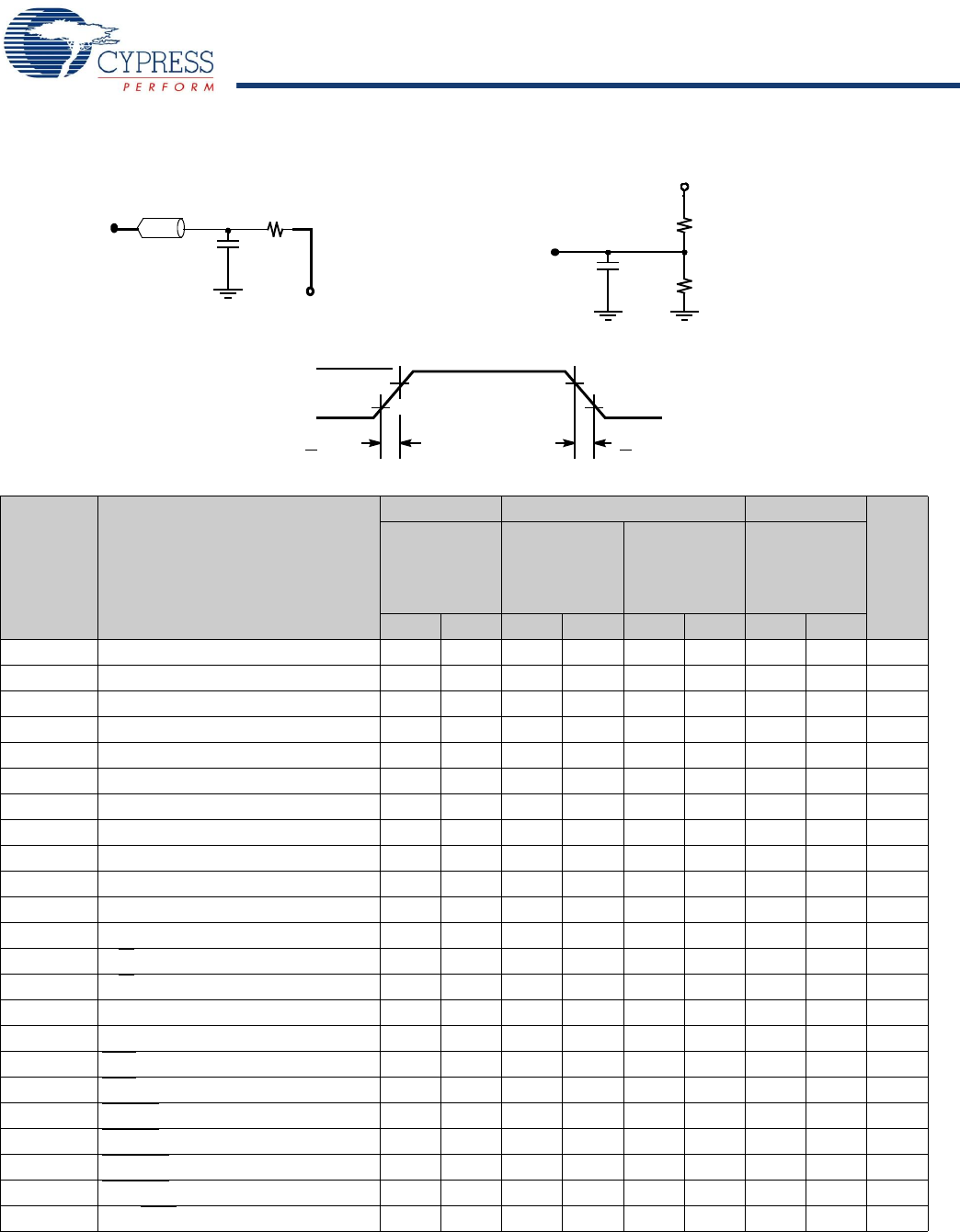

Figure 6. AC Test Load and Waveforms

Switching Characteristics Over the Operating Range

Parameter Description

-167 -133 -100

Unit

CYD01S36V

CYD02S36V/

CYD02S36VA

CYD04S36V

CYD09S36V

CYD01S36V

CYD02S36V

CYD04S36V

CYD09S36V

CYD18S36V CYD18S36V

Min Max Min Max Min Max Min Max

f

MAX2

Maximum Operating Frequency 167 133 133 100 MHz

t

CYC2

Clock Cycle Time 6.0 7.5 7.5 10.0 ns

t

CH2

Clock HIGH Time 2.7 3.0 3.4 4.5 ns

t

CL2

Clock LOW Time 2.7 3.0 3.4 4.5 ns

t

R

[30]

Clock Rise Time 2.0 2.0 2.0 3.0 ns

t

F

[30]

Clock Fall Time 2.0 2.0 2.0 3.0 ns

t

SA

Address Setup Time 2.3 2.5 2.2 2.7 ns

t

HA

Address Hold Time 0.6 0.6 1.0 1.0 ns

t

SB

Byte Select Setup Time 2.3 2.5 2.2 2.7 ns

t

HB

Byte Select Hold Time 0.6 0.6 1.0 1.0 ns

t

SC

Chip Enable Setup Time 2.3 2.5 NA NA ns

t

HC

Chip Enable Hold Time 0.6 0.6 NA NA ns

t

SW

R/W Setup Time 2.3 2.5 2.2 2.7 ns

t

HW

R/W Hold Time 0.6 0.6 1.0 1.0 ns

t

SD

Input Data Setup Time 2.3 2.5 2.2 2.7 ns

t

HD

Input Data Hold Time 0.6 0.6 1.0 1.0 ns

t

SAD

ADS Setup Time 2.3 2.5 NA NA ns

t

HAD

ADS Hold Time 0.6 0.6 NA NA ns

t

SCN

CNTEN Setup Time 2.3 2.5 NA NA ns

t

HCN

CNTEN Hold Time 0.6 0.6 NA NA ns

t

SRST

CNTRST Setup Time 2.3 2.5 NA NA ns

t

HRST

CNTRST Hold Time 0.6 0.6 NA NA ns

t

SCM

CNT/MSK Setup Time 2.3 2.5 NA NA ns

R1 = 590 Ω

R2 = 435 Ω

C = 5 pF

(b) Three-state Delay (Load 2)

90%

10%

3.0V

Vss

90%

10%

<2ns <2ns

ALL INPUT PULSES

3.3V

V

TH

= 1.5V

R = 50Ω

Z

0

= 50Ω

(a) Normal Load (Load 1)

C = 10 pF

OUTPUT

OUTPUT

Note

30.Except JTAG signals (t

r

and t

f

< 10 ns [max.]).

[+] Feedback