RX

-

8581

SA

/

JE

/

NB

Page - 13 MQ372-02

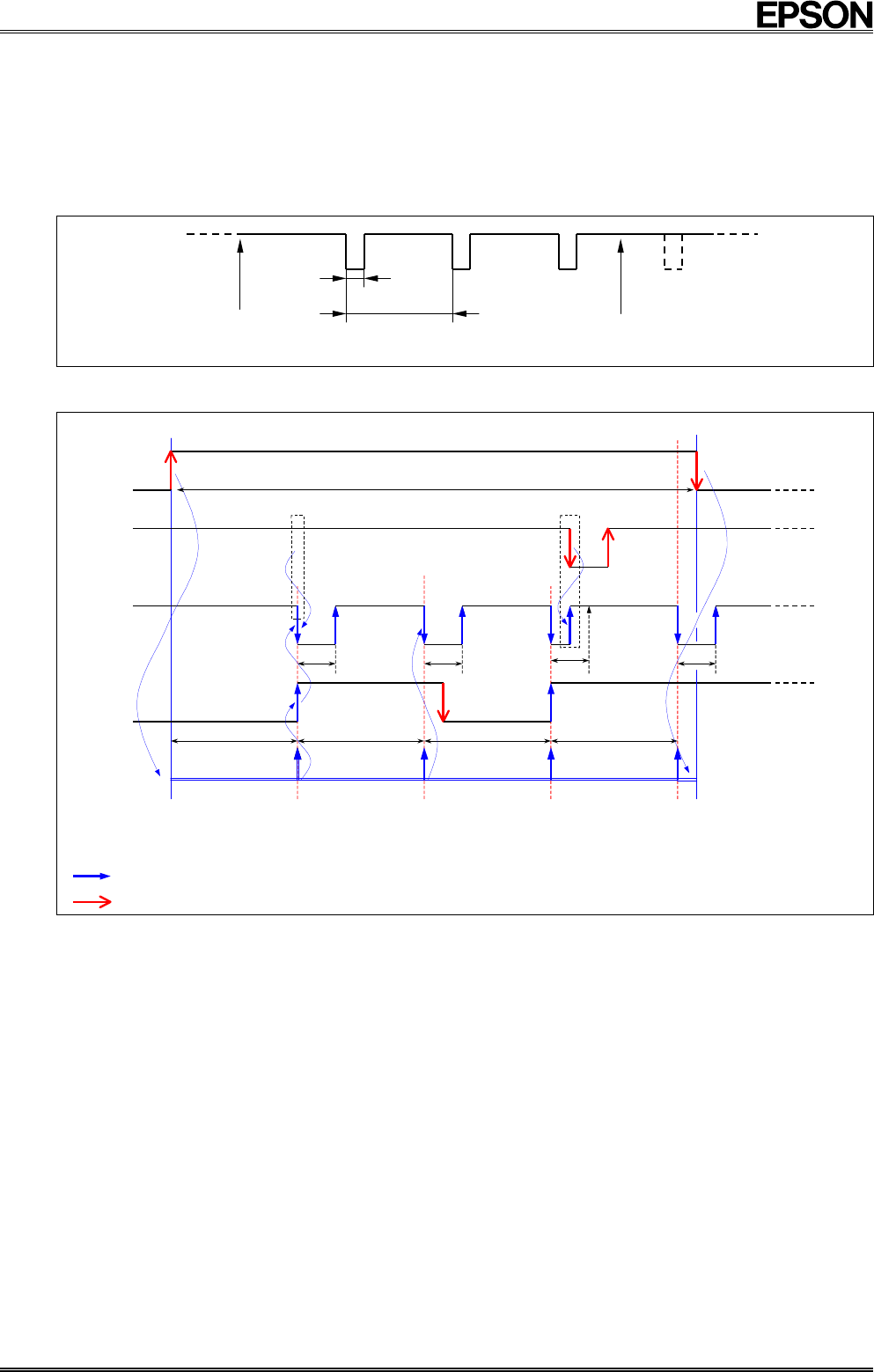

8.3. Fixed-cycle Timer Interrupt Function

The fixed-cycle timer interrupt generation function generates an interrupt event periodically at any fixed cycle set

between 244.14 µs and 4095 minutes.

When an interrupt event is generated, the /INT pin goes to low level and "1" is set to the TF bit to report that an

event has occurred. (However, when a fixed-cycle timer interrupt event has been generated low-level output from

the /INT pin occurs only when the value of the control register's TIE bit is "1". Up to 7.8 ms after the interrupt

occurs, the /INT status is automatically cleared (/INT status changes from low-level to Hi-Z).

∗

Example of

/INT operation

TIE = " 1 "

TE

=

"

0

"

→

"

1

"

7.8ms

(Max.)

period

TIE = " 1 " → " 0 "

8.3.1. Diagram of fixed-cycle timer interrupt function

TIE bit

/INT output

TF bit

Event occurs

TE bit

tRTN

tRTNtRTN

p

eriod

p

eriod

p

eriod

tRTN

p

eriod

" 1"

" 0 "

" 1 "

" 0"

Hi -z

" L"

" 1"

" 0"

∗

Even when the TF

bit is cleared to zero,

the /INT status does

not change.

∗

Even when the TE bit is

cleared to zero, /INT

remains low during the

tRTN time.

Operation of fixed-cycle timer

∗

When the TE bit value changes from

"0"

to "1"

the fixed-cycle timer function starts.

The counter always starts counting down from the preset value when the TE value changes from "0" to "1".

RTC internal operation

Write operation

Fixed-cycle timer starts Fixed-cycle timer stops

(1)

(1)

(2)

• • •

001

h

→

000

h

(3)

(4)

(5)

"

1

"

(6)

(7)

(7)

(7)

(8)

(9)

(1) When a "1" is written to the TE bit, the fixed-cycle timer countdown starts from the preset value.

(2) A fixed-cycle timer interrupt event starts a countdown based on the countdown period (source clock). When

the count value changes from 001h to 000h, an interrupt event occurs.

∗ After the interrupt event that occurs when the count value changes from 001h to 000h, the counter

automatically reloads the preset value and again starts to count down. (Repeated operation)

(3) When a fixed-cycle timer interrupt event occurs, "1" is written to the TF bit.

(4) When the TF bit = "1" its value is retained until it is cleared to zero.

(5) If the TIE bit = "1" when a fixed-cycle timer interrupt occurs, /INT pin output goes low.

∗ If the TIE bit = "0" when a fixed-cycle timer interrupt occurs, /INT pin output remains Hi-Z.

(6) Output from the /INT pin remains low during the tRTN period following each event, after which it is

automatically cleared to Hi-Z status.

∗ /INT is again set low when the next interrupt event occurs.

(7) When a "0" is written to the TE bit, the fixed-cycle timer function is stopped and the /INT pin is set to Hi-Z

status.

∗ When /INT = low, the fixed-cycle timer function is stopped. The tRTN period is the maximum amount of time

before the /INT pin status changes from low to Hi-Z.

(8) As long as /INT = low, the /INT pin status does not change when the TF bit value changes from "1" to "0".

(9) When /INT = low, the /INT pin status changes from low to Hi-Z as soon as the TIE bit value changes from "1" to

"0".