35

2 System Board

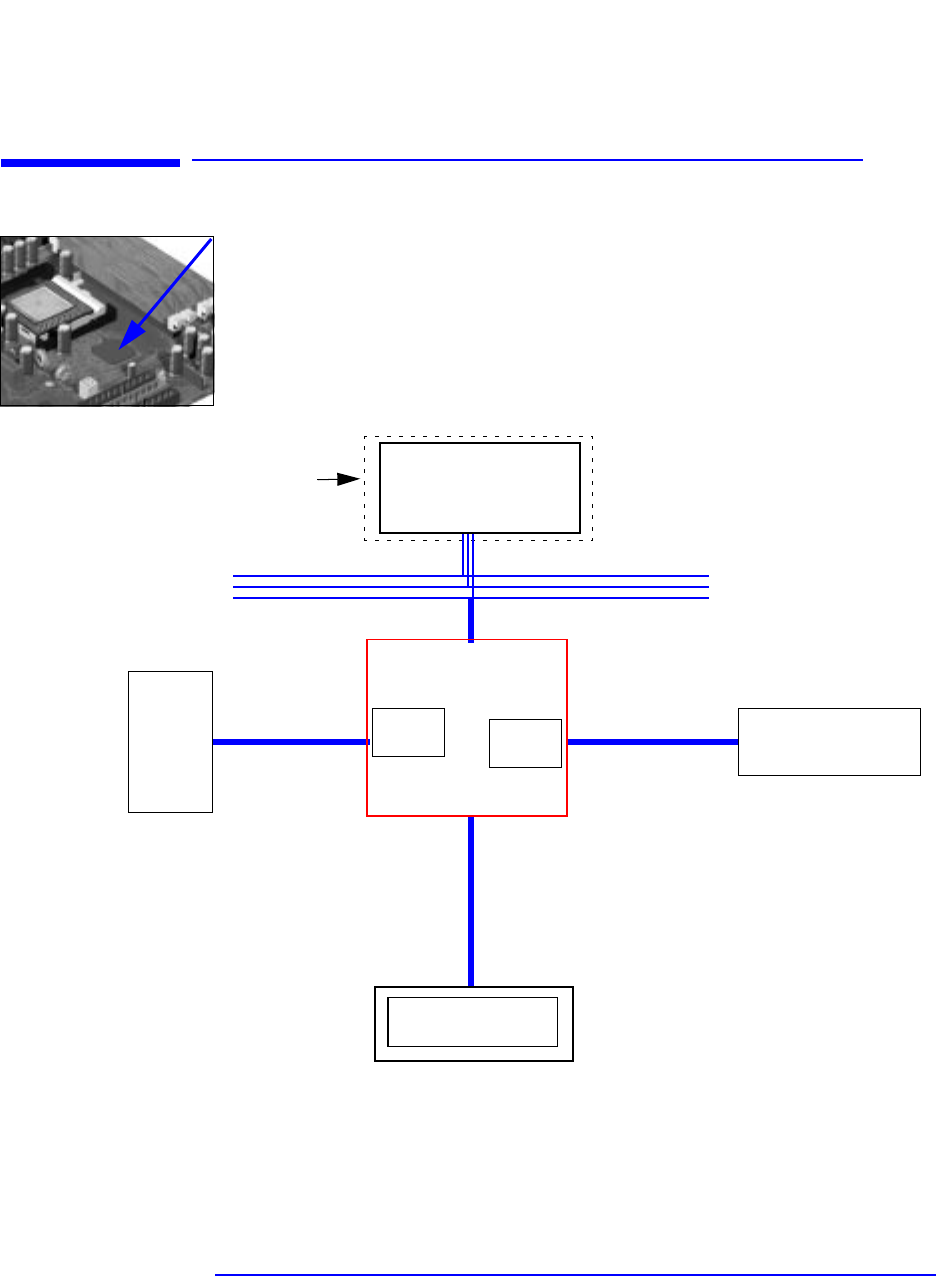

Memory Controller Hub (82850)

Memory Controller Hub (82850)

The MCH Host Bridge/Controller is contained in a 615-pin Organic Land

Grid Array (OLGA) package and is the bridge between the System bus,

Dual Rambus bus (main memory), AGP 4x (graphic) bus and Hub Link 8-

bit.

The following figure shows an example of the system block diagram using

the MCH.

I850 Memory

Controller Hub (MCH)

82850

Dual Rambus Bus

Address (36)

Control

Data (64)

AGP 4x Bus

(133 MHz (1 GB MB/s

data transfer rate)

HUB LINK 8

(266 MB/s data

transfer rate)

I/O Controller Hub

(ICH2) 82801BA

3.2 GB/s at 400 MHz-

data transfer rate

AGP

Interface

Memory

Controller

1.5V

AGP

PRO

Connector

Socket 423

Intel Pentium 4

Processor

4 onboard RIMM sockets

supporting RDRAM memory.

100 MHz two-way System Bus

(Data Bus runs at 4 x 100 MHz,

3.2 GB/s transfer rate)