Functional and Operational Characteristics 3-15

Hitachi Universal Storage Platform V/VM User and Reference Guide

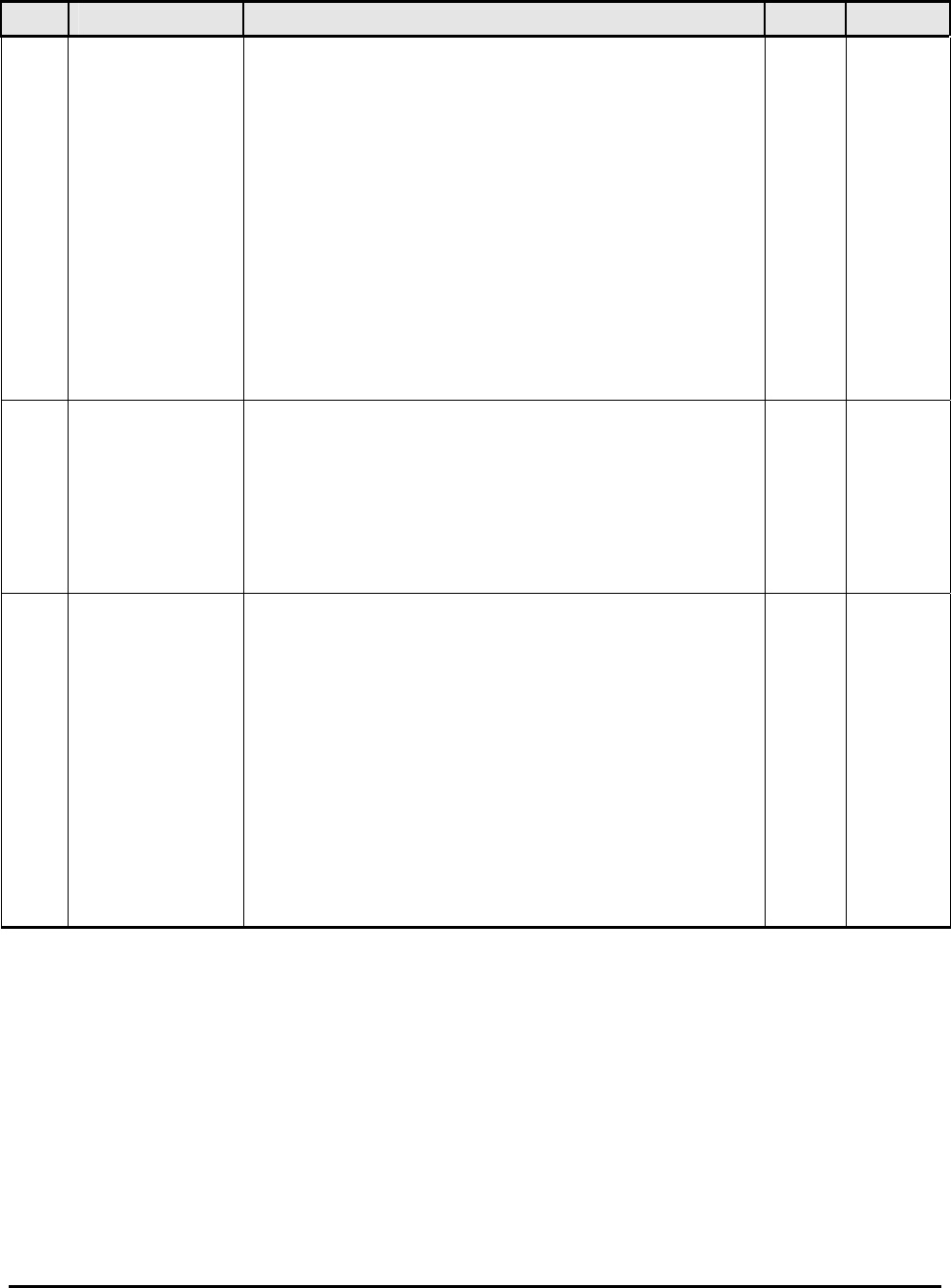

Mode Category Function Default MCU/RCU

493 Mainframe

The CUIR function requires that the SA_ID reported to the host

is unique. The SA_ID value cannot be changed during online

operations. To change the SA_ID value from normal to unique,

set mode 493 to ON and then perform a power cycle*. Setting

mode 493 to ON without performing a power cycle does not

enable the function.

*Power cycle includes PS-OFF/ON (volatile/non-volatile), start-

up after breaker OFF/ON, or offline micro-program exchange.

Mode 493 = ON: When mode 493 is ON and a power cycle is

performed, a unique SA_ID value for each port is reported to

the host.

Mode 493 = OFF: When mode 493 is OFF and a power cycle is

performed, and 2107 port is not set, normal SA_ID values are

reported to the host. When 2107 emulation is set, the SA_ID

value of mainframe PCB port remains unique even after setting

mode 493 to OFF and then performing a power cycle.

Caution: Power cycle is required.

OFF –

494 Mainframe Enables CUIR processing when replacing a FICON PCB.

Mode 494 = ON: CUIR processing is available when replacing a

FICON PCB, but only when mode 493 is ON and a power cycle*

is performed to enable the SA_ID unique mode.

*Power cycle includes PS-OFF/ON (volatile/non-volatile), start-

up after breaker OFF/ON, or offline micro-program exchange.

Mode 494 = OFF: CUIR processing is not available.

Caution: Power cycle is required.

OFF –

498 OPEN One path performance improvement for the OPEN random read.

Mode 498 = ON: One path performance improvement for the

OPEN random read is available.

Mode 498 = OFF: One path performance improvement for the

OPEN random read is not available.

Notes:

When mode 498 is ON, the maximum performance of CHP is

improved, which icreases the number of I/Os to the

back-end (DKP, HDD, external initiator MP, external

storage). Because of this, back-end performance must be

checked to make sure it is sufficient. If back-end

performance is insufficient, a timeout may occur due to a

bottleneck in the back-end.

When a bottleneck occurs in the back-end, the performance

may be worse than when mode 498 is OFF.

OFF –