Intel

®

80303 and 80302 I/O Processors Specification Update 13

Errata

Nominally, the emul multiplies two 32-bit operands to produce a long ordinal (64-bit) result stored

in two adjacent registers. When the errata occurs, the low-order register receives the correct value,

but the high-order register becomes scoreboarded indefinitely. The scoreboarded register is always

odd-numbered (i.e., g1, g3, g5, ..., r7, r9, r11, ...) since the emul instruction always directs the

high-order result to the odd-numbered register of the destination pair.

In some cases, the result of the mulo or muli instruction is corrupted, too, but such has never been

observed apart from the scoreboard failure. Once the scoreboard failure has occurred, subsequent

mulo or muli instructions that are separated by load instructions can also produce faulty results in

some cases. The details of this secondary behavior has not been studied as thoroughly as the

primary scoreboarding issue.

When the scoreboard stalls the processor, higher-level processes, such as higher-priority interrupts

and faults, can run as normal unless they access the scoreboarded register and also stall.

Not all 80303 processors have been observed to exhibit this errata.

Implication: Systems containing this instruction sequence may exhibit sporadic and unrepeatable stall failures

depending on where these instructions appear in the executable memory image and the runtime

dynamics as they affect the Icache.

Workaround: Avoid this sequence of instructions in systems that employ the instruction cache.

Status: NoFix. Refer to Summary Table of Changes to determine the affected stepping(s).

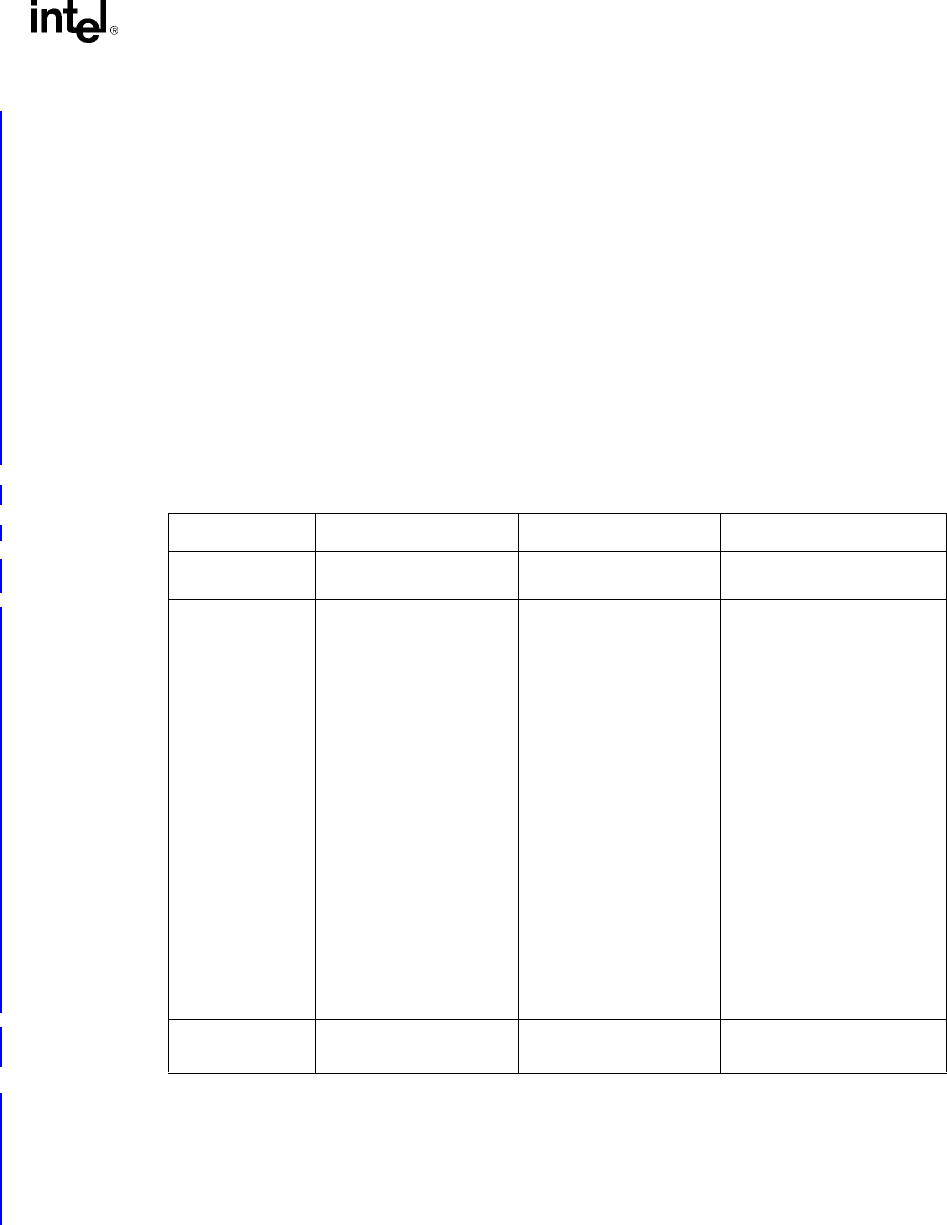

Table 1. Instruction Versions that Can Produce a Scoreboard Failure in this Sequence

Instruction Data Type Addressing Mode Format

1. Extended

Multiply

All n/a emul reg/lit, reg/lit, reg

2. Load

•Word - ld

• Ordinal short - ldos

• Integer short - ldis

• Ordinal byte - ldob

• Integer byte - ldib

• Absolute

Displacement

• Register Indirect with

Displacement

• Index with

Displacement

ld exp, reg

ld exp(reg), reg

ld exp[reg*scale], reg

ldos exp, reg

ldos exp(reg), reg

ldos exp[reg*scale], reg

ldis exp, reg

ldis exp(reg), reg

ldis exp[reg*scale], reg

ldob exp, reg

ldob exp(reg), reg

ldob exp[reg*scale], reg

ldib exp, reg

ldib exp(reg), reg

ldib exp[reg*scale], reg

3. Multiply • Ordinal

• Integer

n/a

mulo reg/lit, reg/lit, reg

muli reg/lit, reg/lit, reg