Intel

®

80303 and 80302 I/O Processors Specification Update 35

Documentation Changes

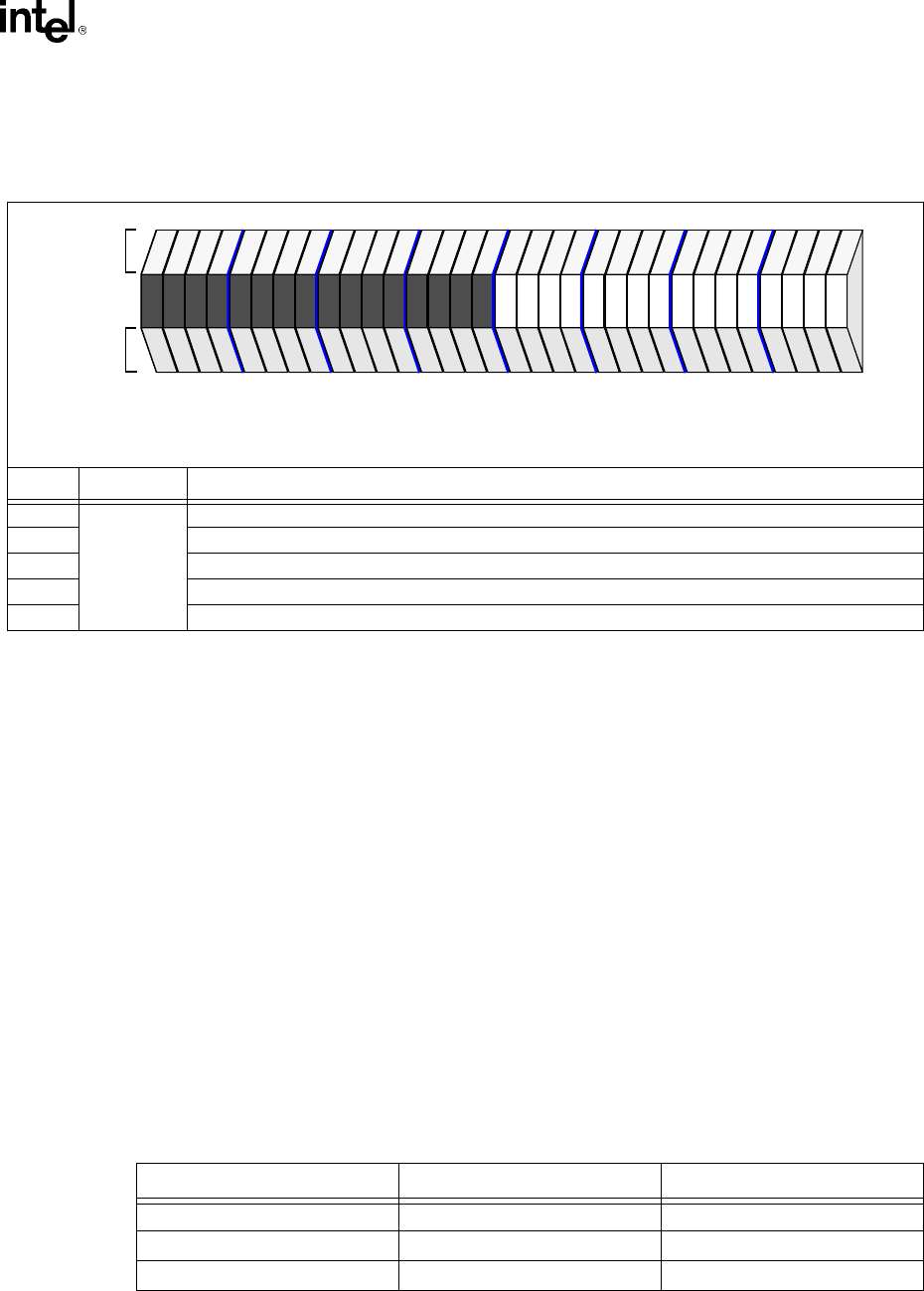

20. Table 8-17 on page 8-38 has incorrect data

Problem: The bit locations for External Interrupt 5 are incorrectly shown as bits '9:4'. It should be '7:4'.

Workaround: Replace Table 8-17 with the following:

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

21. Section 11.2.8 on page 11-5 has incorrect data

Problem: The last sentence in the third paragraph states, 'Specifications for a cold and warm reset can be

found in the 80960RM I/O Processor Data Sheet and the 80960RN I/O Processor Data Sheet.'

This sentence should be removed, it does not pertain to the 80303 I/O processor.

Workaround: Change text to the following: 'The 80303 I/O processor complies with the PCI Local Bus

Specification, Revision 2.2. Reset parameters are defined in this specification.'

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

22. Section 13.2.3.1 on page 13-13 has incorrect data

Problem: The first sentence states, 'The MCU supports an ECC only memory subsystem ranging from 32 to

528 Mbytes.' It should be 512 Mbytes, not 528 Mbytes.

Workaround: Change this sentence to the following: 'The MCU supports an ECC only memory subsystem

ranging from 32 to 512 Mbytes.'

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

23. Table 13-4 on page 13-9 has incorrect data

Problem: Table 13-4 lists incorrect wait states for the flash bus.

Workaround: Replace Table 13-4 with the following:

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

Bit Default Description

31:16

Default

Value loaded

from image

in Control

Table

Reserved (initialize to 0)

15:12 External Interrupt 7 Field - IMAP1.x7

11:8 External Interrupt 6 Field - IMAP1.x6

7:4 External Interrupt 5 Field - IMAP1.x5

3:0 External Interrupt 4 Field - IMAP1.x4

Flash Speed Address-to-Data Wait States Recovery Wait States

<= 55 ns 8 4

<= 115 ns 12 4

<= 175 ns 20 4

PCI

IOP

Attributes

Attributes

28 24 20 16 12 8 4 031

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA= Not Accessible

IMAP1

Intel

®

i960

®

Core internal bus address

FF00 8524H