Intel

®

80303 and 80302 I/O Processors Specification Update 21

Documentation Changes

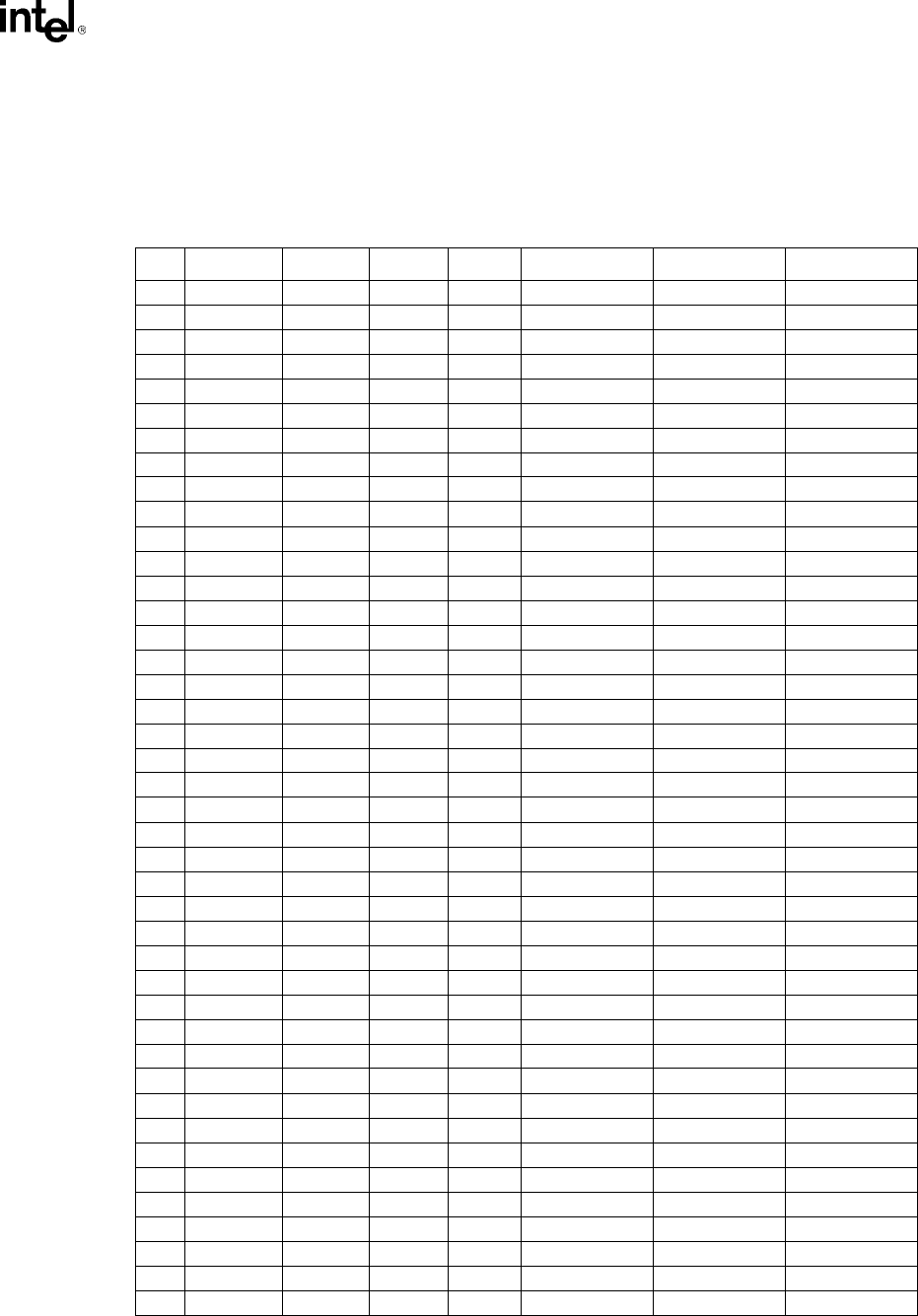

8. Table 24-4 on pg 24-8 is incorrect

Problem: Table 24-4 on pg 24-8 is incorrect.

Workaround: Replace Table 24-4 with the following table:

Table 24-4. Intel

® 80303 I/O Processor Boundary Scan Register Bit Order (Sheet 1 of 10)

# Cell Type Name Function Safe bit Control Signal Disable Value Disable Result

"0 (CBSC_1, scl, bidir, X, 1, 1, Z)," &

"1 (BC_1, *, control, 1)," &

"2 (CBSC_1, sda, bidir, X, 3, 1, Z)," &

"3 (BC_1, *, control, 1)," &

"4 (BC_1, rale, output3, X, 111, 1, Z)," &

"5 (BC_1, roez, output3, X, 111, 1, Z)," &

"6 (CBSC_1, rad(15), bidir, X, 7, 0, Z)," &

"7 (BC_1, *, control, 0)," &

"8 (BC_1, rcez(1), output3, X, 9, 0, Z)," &

"9 (BC_1, *, control, 0)," &

"10 (BC_1, rcez(0), output3, X, 11, 0, Z)," &

"11 (BC_1, *, control, 0)," &

"12 (CBSC_1, rad(6), bidir, X, 28, 1, Z)," &

"13 (BC_1, rwez, output3, X, 111, 1, Z)," &

"14 (CBSC_1, rad(9), bidir, X, 18, 0, Z)," &

"15 (CBSC_1, rad(10), bidir, X, 16, 0, Z)," &

"16 (BC_1, *, control, 0)," &

"17 (CBSC_1, rad(11), bidir, X, 18, 0, Z)," &

"18 (BC_1, *, control, 0)," &

"19 (CBSC_1, rad(13), bidir, X, 20, 0, Z)," &

"20 (BC_1, *, control, 0)," &

"21 (CBSC_1, rad(12), bidir, X, 22, 0, Z)," &

"22 (BC_1, *, control, 0)," &

"23 (CBSC_1, rad(8), bidir, X, 28, 1, Z)," &

"24 (CBSC_1, rad(14), bidir, X, 25, 0, Z)," &

"25 (BC_1, *, control, 0)," &

"26 (CBSC_1, rad(2), bidir, X, 28, 1, Z)," &

"27 (CBSC_1, rad(1), bidir, X, 28, 1, Z)," &

"28 (BC_1, *, control, 1)," &

"29 (CBSC_1, rad(16), bidir, X, 30, 0, Z)," &

"30 (BC_1, *, control, 0)," &

"31 (CBSC_1, rad(0), bidir, X, 28, 1, Z)," &

"32 (CBSC_1, rad(5), bidir, X, 28, 1, Z)," &

"33 (CBSC_1, rad(4), bidir, X, 28, 1, Z)," &

"34 (CBSC_1, rad(3), bidir, X, 28, 1, Z)," &

"35 (BC_4, nc1, input, X)," &

"36 (CBSC_1, rad(7), bidir, X, 28, 1, Z)," &

"37 (CBSC_1, GPIO(0), bidir, X, 38, 1, Z)," &

"38 (BC_1, *, control, 1)," &

"39 (CBSC_1, GPIO(1), bidir, X, 40, 1, Z)," &

"40 (BC_1, *, control, 1)," &

"41 (CBSC_1, GPIO(2), bidir, X, 42, 1, Z)," &