110 Software Developer’s Manual

EEPROM Interface

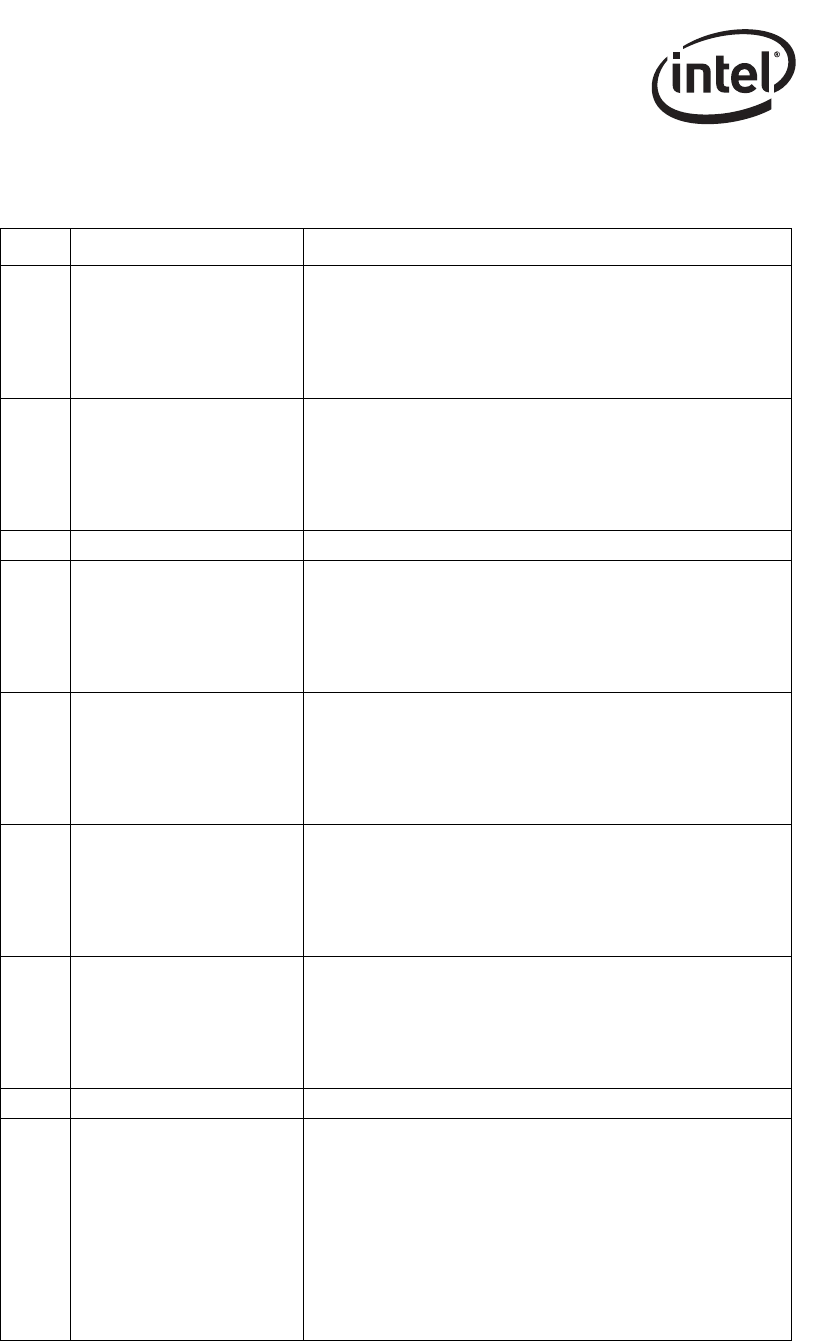

Table 5-8. Software Defined Pins Control (Word 10h, 20h)

Bit Name Description

15

SDPDIR[7]

SDPDIR[3] for the 82541xx

and 82547GI/EI

SDP7(3) Pin - Initial Direction.

Set this bit to 0b (default) to configure the initial hardware value of

the SDP7(3)_IODIR bit in the Extended Device Control Register

(CTRL_EXT) following power up.

Set this bit to 1b if not connected on a board or if used as an

output.

14

SDPDIR[6]

SDPDIR[2] for the 82541xx

and 82547GI/EI

SDP6(2) Pin - Initial Direction.

Set this bit to 0b (default) to configure the initial hardware value of

the SDP6(2)_IODIR bit in the Extended Device Control Register

(CTRL_EXT) following power up.

Set this bit to 1b if not connected on a board or if used as an

output.

13:10 Reserved Set these bits to 0b.

9 SDPDIR[1]

SDP1 Pin - Initial Direction.

Set this bit to 0b (default) to configure the initial hardware value of

the SDP1_IODIR bit in the Extended Device Control Register

(CTRL_EXT) following power up.

Set this bit to 1b if not connected on a board or if used as an

output.

8 SDPDIR[0]

SDP0 Pin - Initial Direction.

Set this bit to 0b (default) to configure the initial hardware value of

the SDP0_IODIR bit in the Extended Device Control Register

(CTRL_EXT) following power up.

Set this bit to 1b if not connected on a board or if used as an

output.

7

SDPVAL[7]

SDPVAL[3] for the 82541xx

and 82547GI/EI

SDP7(3) Pin - Initial Output Value.

Set this bit to 0b (default) to configure the initial power-on value

output on SDP7(3) (when configured as an output) by configuring

the initial hardware value of the SDP7(3)_DATA bit in the Extended

Device Control Register (CTRL_EXT) after power up.

Set this bit to 1b if used as an output.

6

SDPVAL[6]

SDPVAL[2] for the 82541xx

and 82547GI/EI

SDP6(2) Pin - Initial Output Value.

Set this bit to 0b (default) to configure the initial power-on value

output on SDP6(2) (when configured as an output) by configuring

the initial hardware value of the SDP6(2)_DATA bit in the Extended

Device Control Register (CTRL_EXT) after power up.

Set this bit to 1b if used as an output.

5:4 Reserved Set these bits to 0b.

3 EN_PHY_PWR_MGMT

Set this bit to 1b (default) to configure the initial hardware default

value of this bit in the Device Control Register (CTRL) following

power up.

Set this bit to 0b to not configure the initial hardware default value

of this bit in the Device Control Register (CTRL) following power

up.