Receive and Transmit Description

52 Software Developer’s Manual

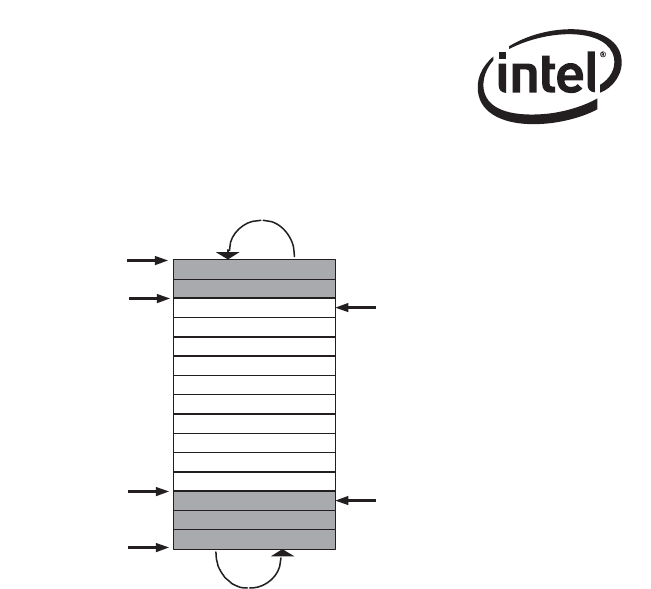

Figure 3-4. Transmit Descriptor Ring Structure

Shaded boxes in Figure 3-4 represent descriptors that have been transmitted but not yet reclaimed

by software. Reclaiming involves freeing up buffers associated with the descriptors.

The transmit descriptor ring is described by the following registers:

• Transmit Descriptor Base Address registers (TDBAL and TDBAH)

These registers indicate the start of the descriptor ring buffer. This 64-bit address is aligned on

a 16-byte boundary and is stored in two consecutive 32-bit registers. TDBAL contains the

lower 32-bits; TDBAH contains the upper 32 bits. Hardware ignores the lower 4 bits in

TDBAL.

• Transmit Descriptor Length register (TDLEN)

This register determines the number of bytes allocated to the circular buffer. This value must

be 128 byte aligned.

• Transmit Descriptor Head register (TDH)

This register holds a value which is an offset from the base, and indicates the in–progress

descriptor. There can be up to 64K descriptors in the circular buffer. Reading this register

returns the value of “head” corresponding to descriptors already loaded in the output FIFO.

• Transmit Descriptor Tail register (TDT)

This register holds a value which is an offset from the base, and indicates the location beyond

the last descriptor hardware can process. This is the location where software writes the first

new descriptor.

The base register indicates the start of the circular descriptor queue and the length register indicates

the maximum size of the descriptor ring. The lower seven bits of length are hard–wired to 0b. Byte

addresses within the descriptor buffer are computed as follows:

address = base + (ptr * 16), where ptr is the value in the hardware head or tail register.

The size chosen for the head and tail registers permit a maximum of 64 K descriptors, or

approximately 16 K packets for the transmit queue given an average of four descriptors per packet.

Circular Buffer

Head

Base + Size

Base

Transmit

Queue

Tail

Owned By

Hardware