Software Developer’s Manual iii

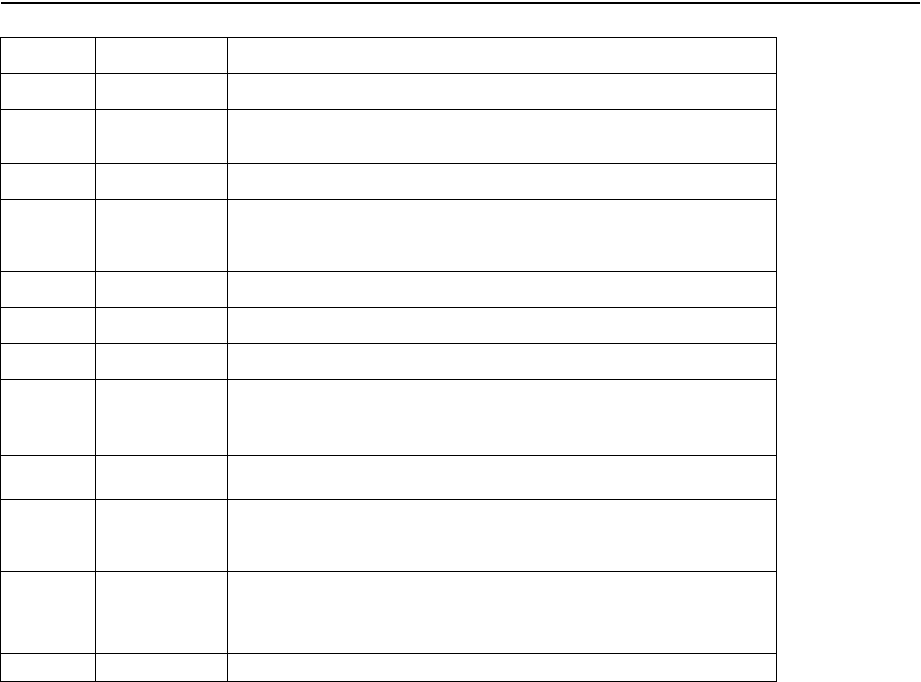

Revision History

Date Version Comments

Mar 2009 4.0

Updated Section 5 (added Table 5-15 “LED Configuration Defaults).

Oct 2008 3.9

Updated section 8.7.4 “Discard PAUSE Frames and Pass MAC Control

Frames”.

June 2008 3.8

Updated EEPROM Word 21h bit descriptions (section 5.6.18).

June 2008 3.7

Updated Sections 13.4.30 and 13.4.31 (added text stating to use the

Interrupt Throttling Register (ITR) instead of registers RDTR and RADV for

applications requiring an interrupt moderation mechanism).

Jan 2007 3.6

Added a note to sections 13.4.20 and 13.4.21 for the 82547Gi/EI.

Sept 2007 3.5

Updated section 13.4.16.

May 2007 3.4

Updated section 6.4.1. Changed acronym “WCR” to “WUC”.

Dec 2006 3.3

Updated Table 13-87. Changed bit 24 settings to:

0b = Cache line granularity.

1b = Descriptor granularity.

June 2006 3.2 Updated Table 13.47. Changed the default setting of reserved bit 3 from 0b

to 1b.

April 2006 3.1 Added bit definitions (bits 9:8) to PHY register PSCON (16d).

Updated Figure 3.2 (added Receive Queue artwork).

Changed 81541ER-C0 to 82541ER-CO in Table 5-1.

Nov 2005 3.0 Updated Device Control/Status, EEPROM Flash Control & Data, Extended

Device Control, and TCTL register bit assignments.

Updated PHY register 00d - 03d, 07d, 09d, 17d - 21d, and 23d bit assign-

ments.

July 2005 2.5 Initial Public Release.