2.2 PCI Express* Interface

This section describes the PCI Express* interface capabilities of the processor. See the

PCI Express Base* Specification 3.0 for details on PCI Express*.

2.2.1 PCI Express* Support

The PCI Express* lanes (PEG[15:0] TX and RX) are fully-compliant to the PCI Express

Base Specification, Revision 3.0.

The Intel

®

Xeon

®

processor with the Server / Workstation PCH supports the

configurations shown in the following table (may vary depending on PCH SKUs).

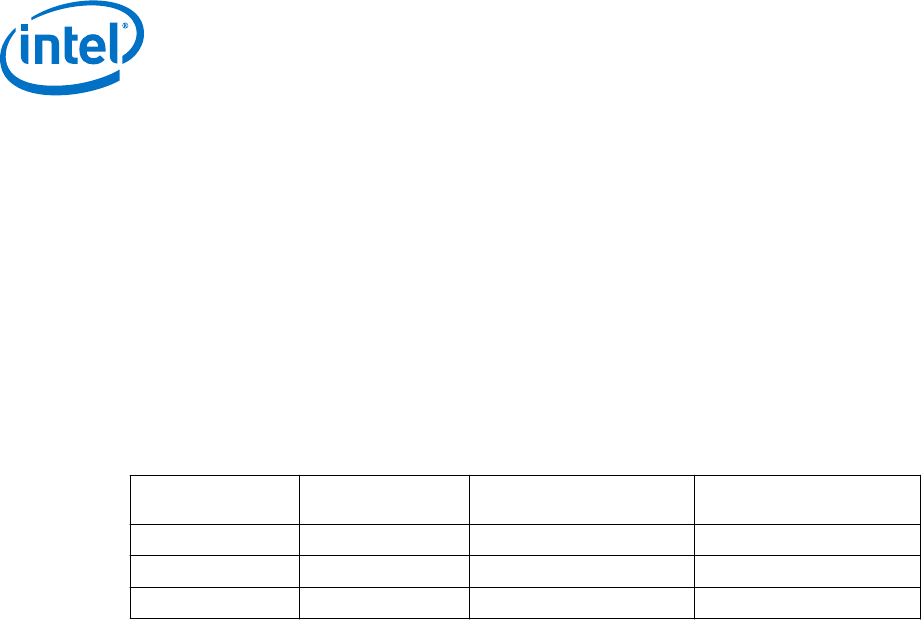

Table 5. PCI Express* Supported Configurations in Server / Workstation Products

Configuration Essential Server Standard Server Advanced Workstation /

Server

1x8, 2x4 I/O I/O GFX, I/O

2x8 I/O I/O GFX, I/O, Dual x8 GFX

1x16 GFX, I/O GFX, I/O GFX, I/O

• The port may negotiate down to narrower widths.

— Support for x16/x8/x4/x2/x1 widths for a single PCI Express* mode.

• 2.5 GT/s, 5.0 GT/s and 8 GT/s PCI Express* bit rates are supported.

• Gen1 Raw bit-rate on the data pins of 2.5 GT/s, resulting in a real bandwidth per

pair of 250 MB/s given the 8b/10b encoding used to transmit data across this

interface. This also does not account for packet overhead and link maintenance.

Maximum theoretical bandwidth on the interface of 4 GB/s in each direction

simultaneously, for an aggregate of 8 GB/s when x16 Gen 1.

• Gen 2 Raw bit-rate on the data pins of 5.0 GT/s, resulting in a real bandwidth per

pair of 500 MB/s given the 8b/10b encoding used to transmit data across this

interface. This also does not account for packet overhead and link maintenance.

Maximum theoretical bandwidth on the interface of 8 GB/s in each direction

simultaneously, for an aggregate of 16 GB/s when x16 Gen 2.

• Gen 3 raw bit-rate on the data pins of 8.0 GT/s, resulting in a real bandwidth per

pair of 984 MB/s using 128b/130b encoding to transmit data across this interface.

This also does not account for packet overhead and link maintenance. Maximum

theoretical bandwidth on the interface of 16 GB/s in each direction simultaneously,

for an aggregate of 32 GB/s when x16 Gen 3.

• Hierarchical PCI-compliant configuration mechanism for downstream devices.

• Traditional PCI style traffic (asynchronous snooped, PCI ordering).

• PCI Express* extended configuration space. The first 256 bytes of configuration

space aliases directly to the PCI Compatibility configuration space. The remaining

portion of the fixed 4-KB block of memory-mapped space above that (starting at

100h) is known as extended configuration space.

• PCI Express* Enhanced Access Mechanism. Accessing the device configuration

space in a flat memory mapped fashion.

• Automatic discovery, negotiation, and training of link out of reset.

Processor—Interfaces

Intel

®

Xeon

®

Processor E3-1200 v3 Product Family

Datasheet – Volume 1 of 2 June 2013

22 Order No.: 328907-001