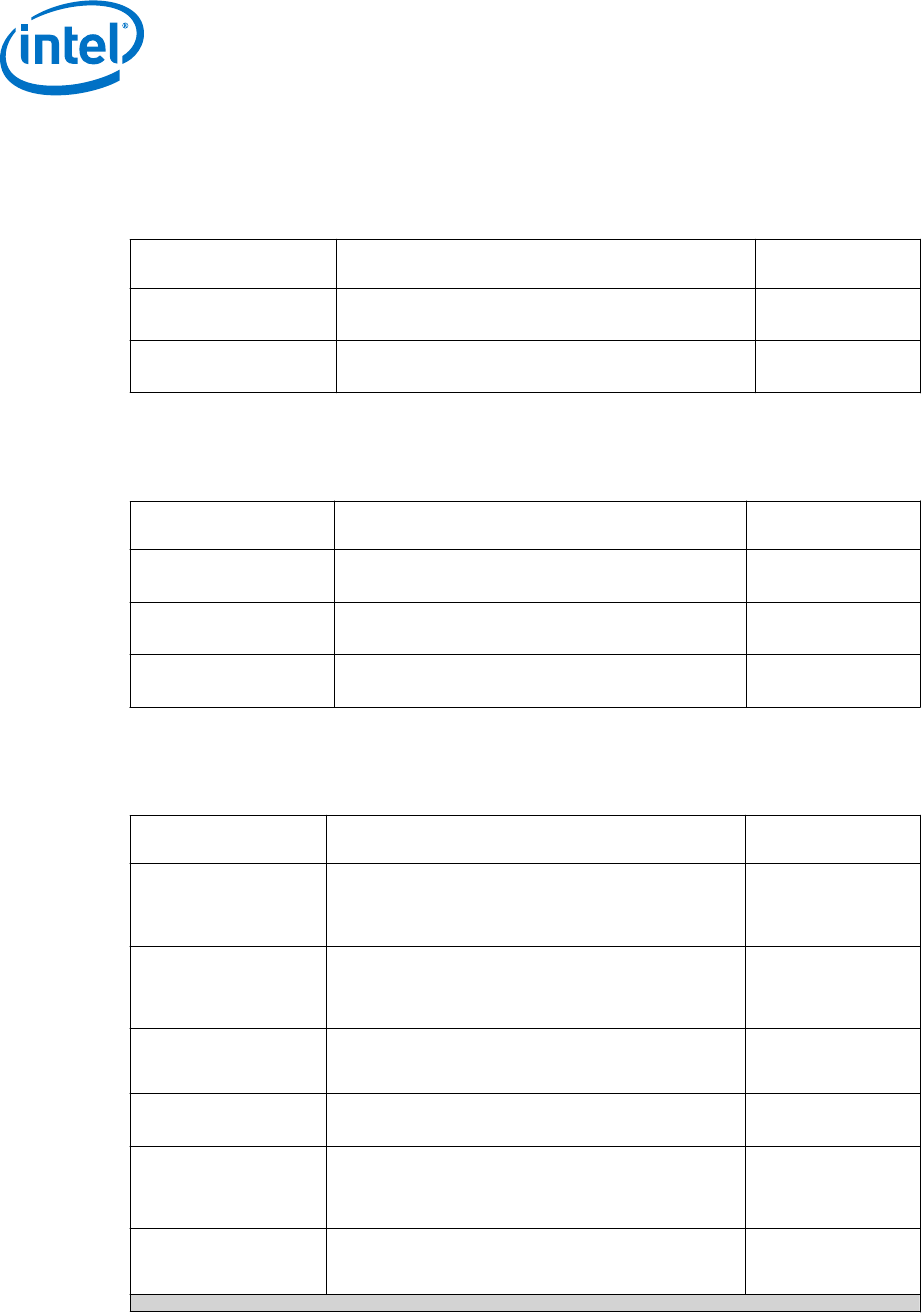

6.6 Direct Media Interface (DMI)

Table 29. Direct Media Interface (DMI) – Processor to PCH Serial Interface

Signal Name Description Direction / Buffer

Type

DMI_RXP[3:0]

DMI_RXN[3:0]

DMI Input from PCH: Direct Media Interface receive

differential pair.

I

DMI

DMI_TXP[3:0]

DMI_TXN[3:0]

DMI Output to PCH: Direct Media Interface transmit

differential pair.

O

DMI

6.7 Phase Locked Loop (PLL) Signals

Table 30. Phase Locked Loop (PLL) Signals

Signal Name Description Direction / Buffer

Type

BCLKP

BCLKN

Differential bus clock input to the processor I

Diff Clk

DPLL_REF_CLKP

DPLL_REF_CLKN

Embedded Display Port PLL Differential Clock In:

135 MHz

I

Diff Clk

SSC_DPLL_REF_CLKP

SSC_ DPLL_REF_CLKN

Spread Spectrum Embedded DisplayPort PLL

Differential Clock In: 135 MHz

I

Diff Clk

6.8 Testability Signals

Table 31. Testability Signals

Signal Name Description Direction / Buffer

Type

BPM#[7:0]

Breakpoint and Performance Monitor Signals:

Outputs from the processor that indicate the status of

breakpoints and programmable counters used for

monitoring processor performance.

I/O

CMOS

DBR#

Debug Reset: This signal is used only in systems where

no debug port is implemented on the system board.

DBR# is used by a debug port interposer so that an in-

target probe can drive system reset.

O

PRDY#

Processor Ready: This signal is a processor output

used by debug tools to determine processor debug

readiness.

O

Asynchronous CMOS

PREQ#

Processor Request: This signal is used by debug tools

to request debug operation of the processor.

I

Asynchronous CMOS

TCK

Test Clock: This signal provides the clock input for the

processor Test Bus (also known as the Test Access

Port). This signal must be driven low or allowed to float

during power on Reset.

I

GTL

TDI

Test Data In: This signal transfers serial test data into

the processor. This signal provides the serial input

needed for JTAG specification support.

I

GTL

continued...

Processor—Signal Description

Intel

®

Xeon

®

Processor E3-1200 v3 Product Family

Datasheet – Volume 1 of 2 June 2013

82 Order No.: 328907-001