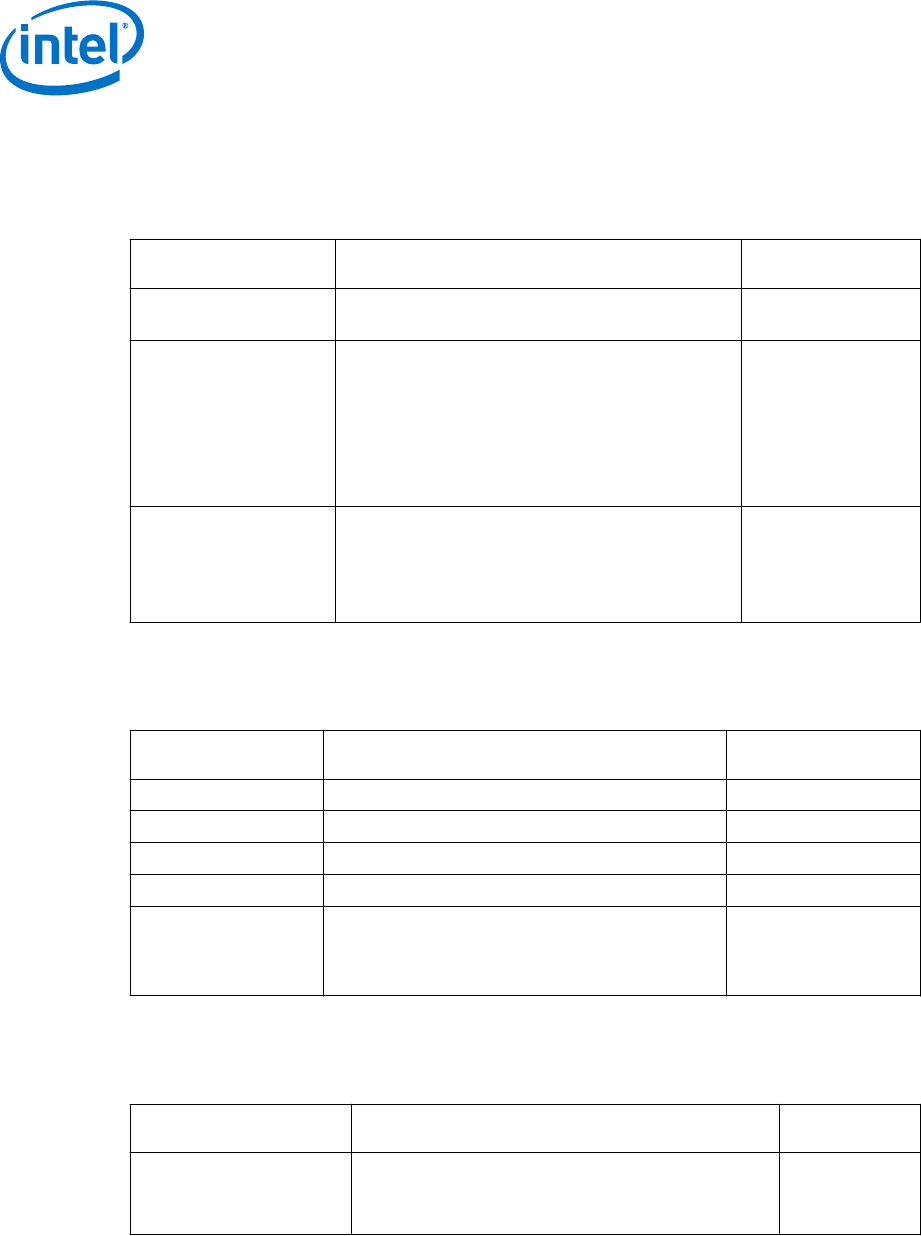

6.10 Power Sequencing

Table 33. Power Sequencing

Signal Name Description Direction / Buffer

Type

SM_DRAMPWROK

SM_DRAMPWROK Processor Input: This signal

connects to the PCH DRAMPWROK.

I

Asynchronous CMOS

PWRGOOD

The processor requires this input signal to be a clean

indication that the V

CC

and V

DDQ

power supplies are

stable and within specifications. This requirement

applies regardless of the S-state of the processor.

'Clean' implies that the signal will remain low (capable

of sinking leakage current), without glitches, from the

time that the power supplies are turned on until they

come within specification. The signal must then

transition monotonically to a high state.

I

Asynchronous CMOS

SKTOCC#

SKTOCC# (Socket Occupied)/PROC_DETECT#:

(Processor Detect): This signal is pulled down

directly (0 Ohms) on the processor package to the

ground. There is no connection to the processor silicon

for this signal. System board designers may use this

signal to determine if the processor is present.

—

6.11 Processor Power Signals

Table 34. Processor Power Signals

Signal Name Description Direction / Buffer

Type

VCC Processor core power rail. Ref

VCCIO_OUT Processor power reference for I/O. Ref

VDDQ Processor I/O supply voltage for DDR3. Ref

VCOMP_OUT Processor power reference for PEG/Display RCOMP. Ref

VIDSOUT

VIDSCLK

VIDALERT#

VIDALERT#, VIDSCLK, and VIDSCLK comprise a three

signal serial synchronous interface used to transfer

power management information between the

processor and the voltage regulator controllers.

Input GTL/ Output Open

Drain

Output Open Drain

Input CMOS

6.12 Sense Pins

Table 35. Sense Pins

Signal Name Description Direction /

Buffer Type

VCC_SENSE

VSS_SENSE

VCC_SENSE and VSS_SENSE provide an isolated, low-

impedance connection to the processor input V

CC

voltage

and ground. They can be used to sense or measure

voltage near the silicon.

O

A

Processor—Signal Description

Intel

®

Xeon

®

Processor E3-1200 v3 Product Family

Datasheet – Volume 1 of 2 June 2013

84 Order No.: 328907-001