User’s Manual

ESM-2740/2743 User’s Manual

31

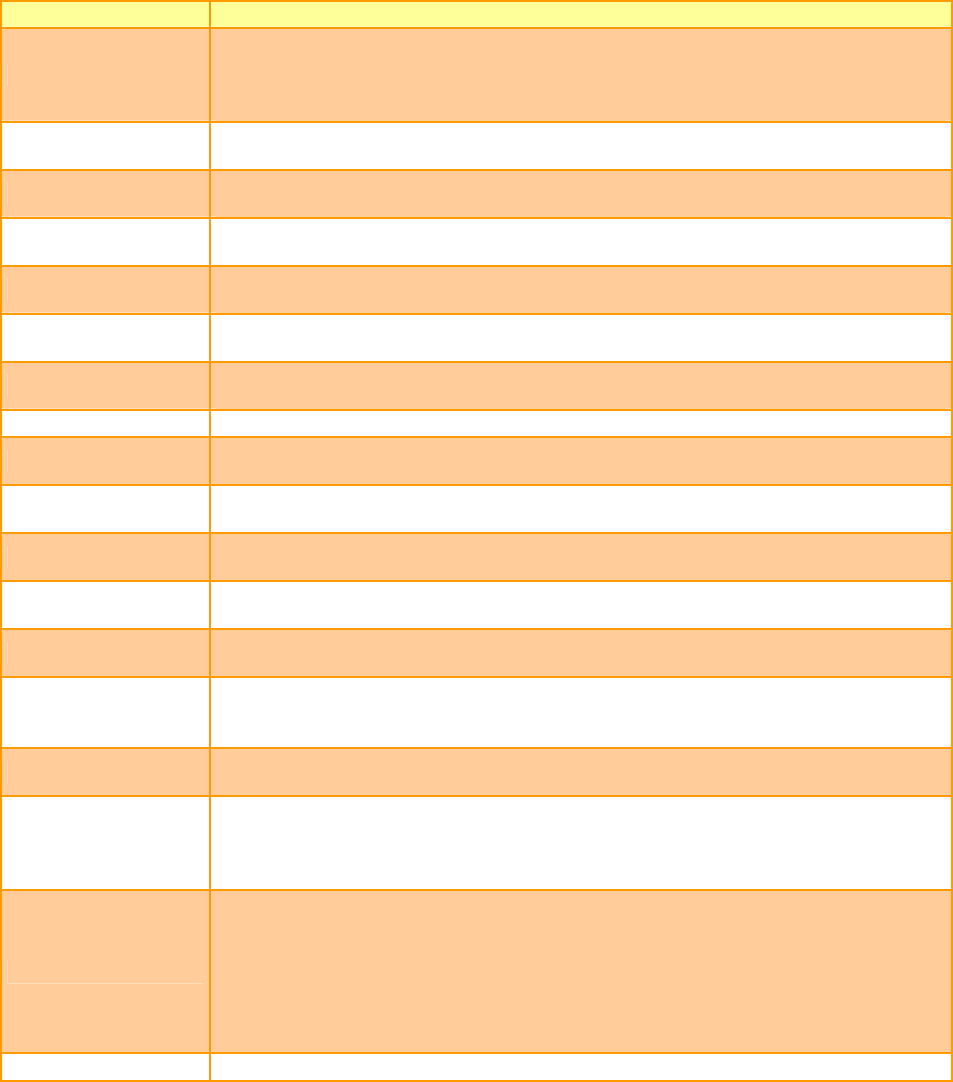

2.4.3 Signal Description – ETX Connector X1 (ETXA)

2.4.3.1 PCI Signals

Signal Signal Description

PCICLK [1:4]

PCI clock outputs for up to 4 external PCI slots or devices.

The baseboard designer should route these clocks for 1300pS total delay from the

ETX connector pin to the clock pin of the PCI device. See the ETX Design Guide

for typical route length calculations.

REQ [0:3]#

Bus Request signals for up to 4 external bus mastering PCI devices. When

asserted, a PCI device is requesting PCI bus ownership from the arbiter.

GNT [0:3]#

Grant signals to PCI Masters. When asserted by the arbiter, the PCI master has

been granted ownership of the PCI bus.

AD [0:31]

PCI Address and Data Bus Lines. These lines carry the address and data

information for PCI transactions.

CBE [0:3]#

PCI Bus Command and Byte Enables. Bus command and byte enables are

multiplexed in these lines for address and data phases, respectively.

PAR

Parity bit for the PCI bus. Generated as even parity across AD [31:0] and CBE

[3:0]#.

SERR#

System Error. Asserted for hardware error conditions such as parity errors

detected in DRAM.

PERR# Parity Error. For PCI operation per exception granted by PCI 2.1 Specification.

LOCK#

Lock Resource Signal. This pin indicates that either the PCI master or the bridge

intends to run exclusive transfers.

DEVSEL#

Device Select. When the target device has decoded the address as its own cycle,

it will assert DEVSEL#.

TRDY#

Target Ready. This pin indicates that the target is ready to complete the current

data phase of a transaction.

IRDY#

Initiator Ready. This signal indicates that the initiator is ready to complete the

current data phase of a transaction.

STOP#

Stop. This signal indicates that the target is requesting that the master stop the

current transaction.

FRAME#

Cycle Frame of PCI Buses. This indicates the beginning and duration of a PCI

access. The access will be either an output driven by the Northbridge on behalf of

the CPU, or an input during PCI master access.

PCIRST#

PCI Bus Reset. This is an output signal to reset the entire PCI Bus. This signal is

asserted during system reset.

INTRA#,

INTRB#,

INTRC#,

INTRD#

PCI interrupts.

These interrupts are sharable and are typically wired in rotation to PCI slots or

devices.

IDSEL

This pin is not present on the ESM-2740/2743 module connector, but it is present

on each PCI slot connector or device. IDSEL is an input to the device that is used

to set the device’s configuration address for PCI configuration cycles. The IDSEL

pin of each device is typically connected to one of the AD lines in order to set a

unique configuration address.

In ETX systems, the four external bus slots or devices are assumed to use

AD[19:22] for IDSEL connections.

PME# Power management event..