User’s Manual

ESM-2740/2743 User’s Manual

41

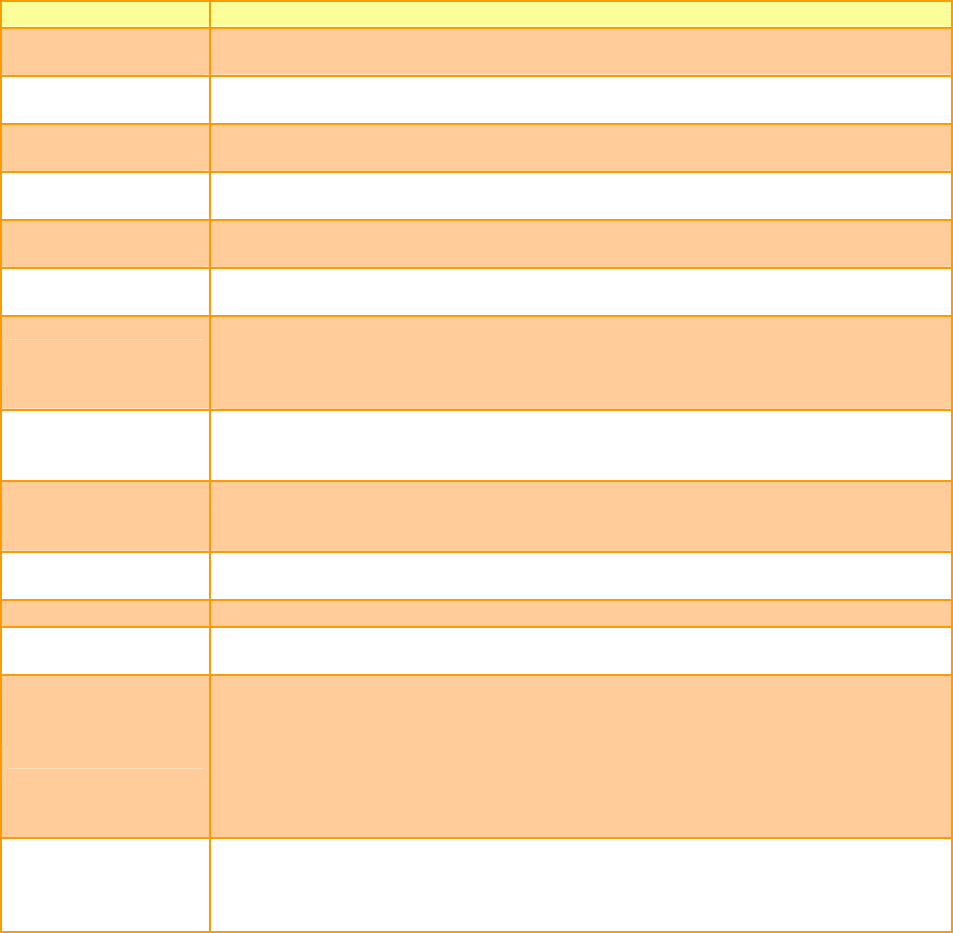

2.4.9.2 IDE Signals

Signal Signal Description

PIDE_D[0:15]/

SIDE_D[0:15]

IDE Data Bus.

PIDE_A[0:2]/

SIDE_A[0:2]

IDE Address Bus.

PIDE_CS1#/

SIDE_CS1#

IDE Chip Select 1. This is the Chip Select 1 command output pin that enables the

IDE device to watch the Read/Write Command.

PIDE_CS3#/

SIDE_CS3#

IDE Chip Select 3. This is the Chip Select 3 command output pin that enables the

IDE device to watch the Read/Write Command.

PIDE_DRQ/

SIDE_DRQ

IDE DMA Request for IDE Master. This signal is asserted by an IDE device. It will

be active-high in DMA or Ultra-33 mode and always be inactive-low in PIO mode.

PIDED_AK#/

SIDED_AK#

IDE DACK# for IDE Master. This signal grants the IDE DMA request to begin the

IDE Master Transfer in DMA or Ultra-33 mode.

PIDE_RDY/

SIDE_RDY

IDE Ready. This is the input pin from the IDE Channel. It indicates that the IDE

device is ready to terminate the IDE command in PIO mode. The IDE device can

de-assert this input to expand the IDE command if the device is not ready. In

Ultra-33 mode, this pin has different functions.

PIDE_IOR#/

SIDE_IOR#

IDE IOR# Command. This is the IOR# command output pin used to tell the IDE

device to assert the Read Data in PIO and DMA mode. In Ultra-33 mode, this pin

has different functions.

PIDE_IOW#/

SIDE_IOW#

IDE IOW# Command. This is the IOW# command output pin used to notify the IDE

device that the available Write Data is already asserted by the IDE Busmaster in

PIO and DMA mode. In Ultra-33 mode, this pin has different functions.

PIDE_INTRQ/

SIDE_INTRQ

Interrupt request signal from the IDE device.

HDRST# Low-active hardware reset (RSTDRV inverted).

DASP_S

Time-multiplexed, open collector output that indicates that a drive is active. Also

used for Master/Slave negotiation on the Secondary IDE channel.

PDIAG_S

The signal is used for Master/Slave negotiation on the Secondary IDE channel. It is

asserted by the Slave to indicate to a master that the slave has passed its internal

Diagnostic command. If an IDE device such as a Flash Disk exists onboard the

ETX module, this signal must be connected to the PDIAG_S pin of any other

device connected to the Secondary IDE channel. On ETX modules that support

DMA66 or DMA100, this pin may additionally be used to detect the presence of the

80 conductor IDE cable which is required to support these modes.

CBLID_P#

On ETX modules that support DMA66 or DMA100, this pin may be used to detect

the presence of an 80 conductor IDE cable on the primary IDE channel. This

allows BIOS or system software to determine whether to enable high-speed

transfer modes.