3-2 IQ80960RM/RN

Evaluation Board Manual

Hardware Reference

3.2.1 SDRAM Performance

The IQ80960RM/RN platform uses 72-bit SDRAM with ECC or 64-bit SDRAM without ECC.

SDRAM allows zero data-to-data wait state operation at 66 MHz. The memory controller unit

(MCU) of the i960

®

RM/RN I/O processor supports SDRAM burst lengths of four. A burst length

of four enables seamless read/write bursting of long data streams, as long as the MCU does not

cross the page boundary. Page boundaries are naturally aligned 2 Kbyte blocks. 72-bit SDRAM

with ECC allows a maximum throughput of 528 Mbytes per second.

Both 16 Mbit and 64 Mbit SDRAM devices are supported. The MCU keeps two pages per bank

open simultaneously for 16 Mbit devices and 4 pages per bank for 64 Mbit devices. Simultaneously

open pages allow for greater performance for sequential access, distributed across multiple internal

bus transactions. Table 3-3 shows read and write examples of a single 8 byte access and for a

multiple 40 byte access.

Note that if ECC is enabled and you attempt a partial write — less than 64 bits — you will incur a

penalty. Because ECC is enabled, the MCU will translate the write into a read-modify-write

transaction. Therefore, for a single byte write the clock count will be 11.

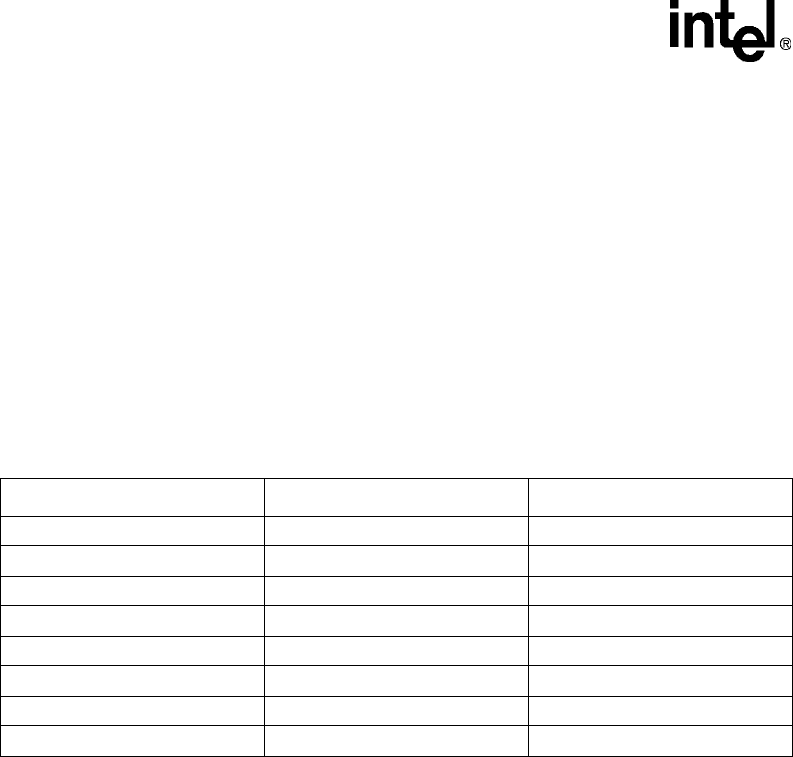

Table 3-3. SDRAM Performance

Cycle Type Table Clocks Performance Bandwidth

Read Page Hit (8 bytes) 7 76 Mbytes/sec

Read Page Miss (8 bytes) 12 44 Mbytes/sec

Read Page Hit (40 bytes) 11 240 Mbytes/sec

Read Page Miss (40 bytes) 16 165 Mbytes/sec

Write Page Hit (8 bytes) 4 132 Mbytes/sec

Write Page Miss (8 bytes) 8 66 Mbytes/sec

Write Page Hit (40 bytes) 8 330 Mbytes/sec

Write Page Miss (40 bytes) 12 220 Mbytes/sec