IQ80960RM/RN

Evaluation Board Manual 3-7

Hardware Reference

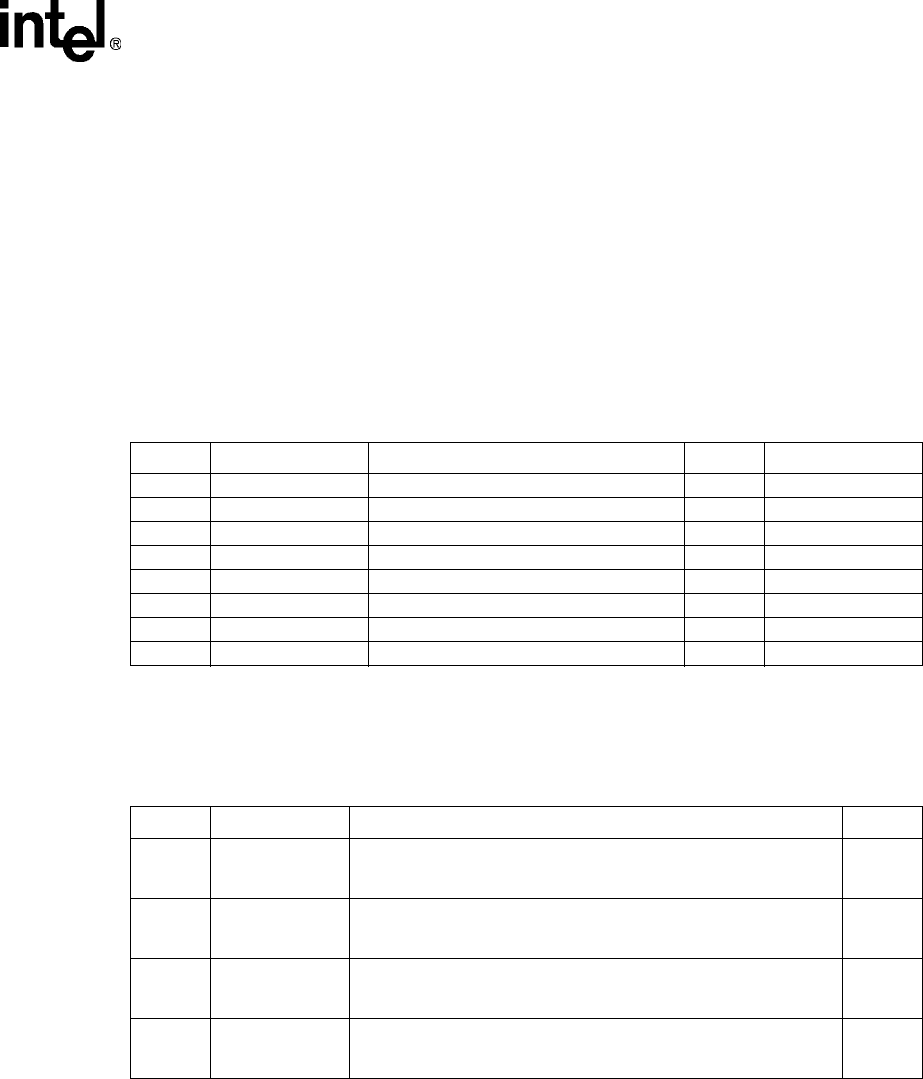

3.9 JTAG Header

The JTAG header allows debugging hardware to be quickly and easily connected to some of the

IQ80960RM/RN processor’s logic signals.

The JTAG header is a 16-pin header. A 3M connector (part number 2516-6002UG) is required to

connect to this header. The pinout for the JTAG header is shown in Table 3-8. The header and

connector are keyed using a tab on the connector and a slot on the header to ensure proper installation.

Each signal in the JTAG header is paired with its own ground connection to avoid the noise problems

associated with long ribbon cables. Signal descriptions are found in the i960

®

RM/RN I/O Processor

Developer’s Manual, 80960RM I/O Processor Data Sheet and the 80960RN I/O Processor Data Sheet.

Table 3-9 describes switch setting options and defaults. These switch settings are sampled at

Primary PCI Reset. See Table 5-1 “Initialization Modes” on page 5-3 for processor initialization

configurations.

Table 3-8. JTAG Header Pinout

Pin Signal Input/Output to 80960RM/RN Pin Signal

1 TRST# IN 2 GND

3 TDI IN 4 GND

5 TDO OUT 6 GND

7TMS IN 8GND

9TCK IN 10GND

11 LCDINIT# IN 12 GND

13 I_RST# OUT 14 GND

15 PWRVLD OUT 16 GND

Table 3-9. Switch S1 Settings

Position Name Description Default

S1-1 RST_MODE#

Determines if the processor is to be held in reset.

ON = hold in rest

OFF = allows processor initialization

OFF

S1-2 RETRY

Determines if the Primary PCI interface will be disabled.

ON = allows Primary PCI configuration cycles to occur

OFF = retries all Primary PCI configuration cycles

OFF

S1-3 32BITMEM_EN#

Notifies Memory Controller of the SDRAM width.

ON = Memory Controller utilizes 32-bit SDRAM access protocol

OFF = Memory Contoller utilizes 64-bit SDRAM access protocol

OFF

S1-4

a

a. This switch is active for IQ80960RN ONLY.

32BITPCI_EN#

Determines whether Secondary PCI bus is a 32- or 64-bit bus.

ON = indicates Secondary PCI bus is a 32-bit bus

OFF = indicates Secondary PCI bus is a 64-bit bus

OFF