Quick Start Guide—Intel

®

IXDP465 Development Platform

AN Intel

®

IXDP465 Development Platform May 2005

Order Number: 305825, Revision: 002 15

7.2 Intel

®

IXP465 Network Processor/DDR Module Jumpers

Figure 4 identifies the jumper locations and Table 5 describes the jumper settings for the Intel

®

IXP465 Network Processor/DDR module.

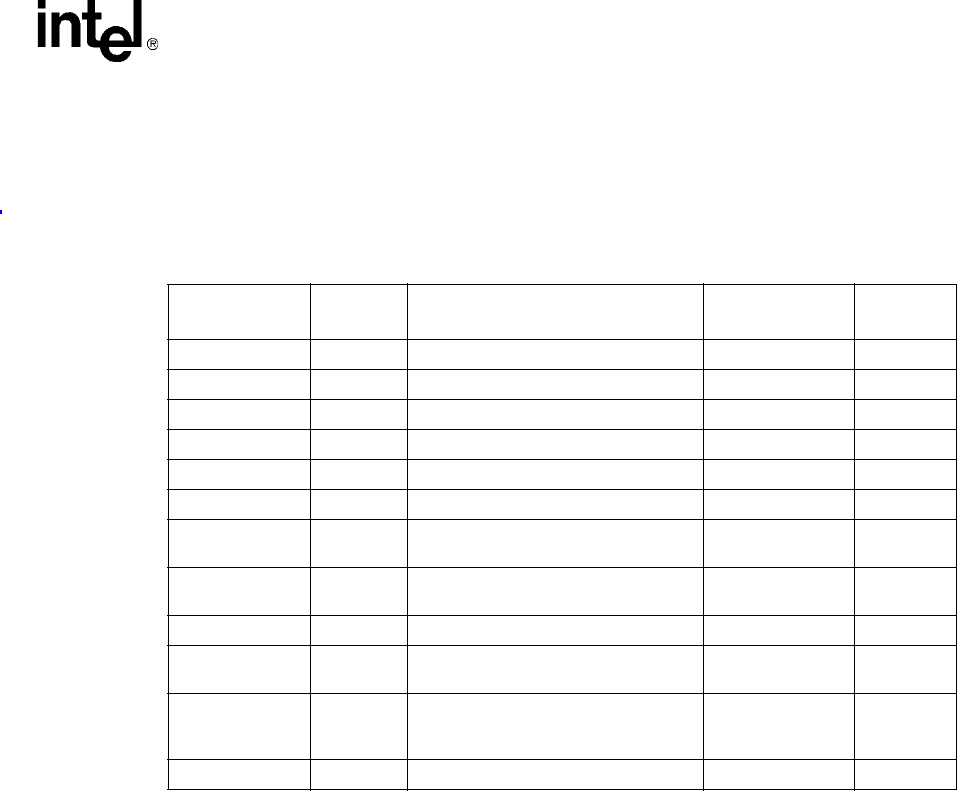

Table 5. Intel

®

IXP465 Network Processor/DDR Module Jumper Descriptions and Default

Settings

Board Location

(See Figure 4)

Ref ID

Jumper Description

for Installed State

Default Settings

Quick Start

Check?

SCL P4 Selects I2C pin, instead of GPIO Shunt 1-2. F

SDA P2 Selects I2C pin, instead of GPIO Shunt 1-2. F

IXP 3.3V JP45 Enables monitoring of +3.3V current Not installed. F

XTAL OUT JP50 Reserved Not installed. F

XTAL IN JP49 Reserved Not installed. F

BYPSSCLK JP41 Connects oscillator to OSC_IN Installed. F

REFCLK JP1

Enables Spreadspectrum clock

reference

Not installed. F

SSCLK JP2

Connects Spreadspectrum clock to

OSC_IN

Not installed. F

ENSSCLK JP44 Enables Spreadspectrum clock output Not installed. F

IXP COREV JP47

Enables monitoring of +1.3V/+1.4V

current

Not installed. F

667 MHz JP48

Enables selection of +1.3V as core

voltage, instead of +1.4V as required

for 667 MHz operation

Installed. F

IXP 2.5V JP46 Enables monitoring of +2.5V current Not installed. F