E‐14HardwareReferenceManual www.picocomputing.com PicoComputing,Inc.

30

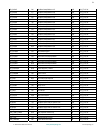

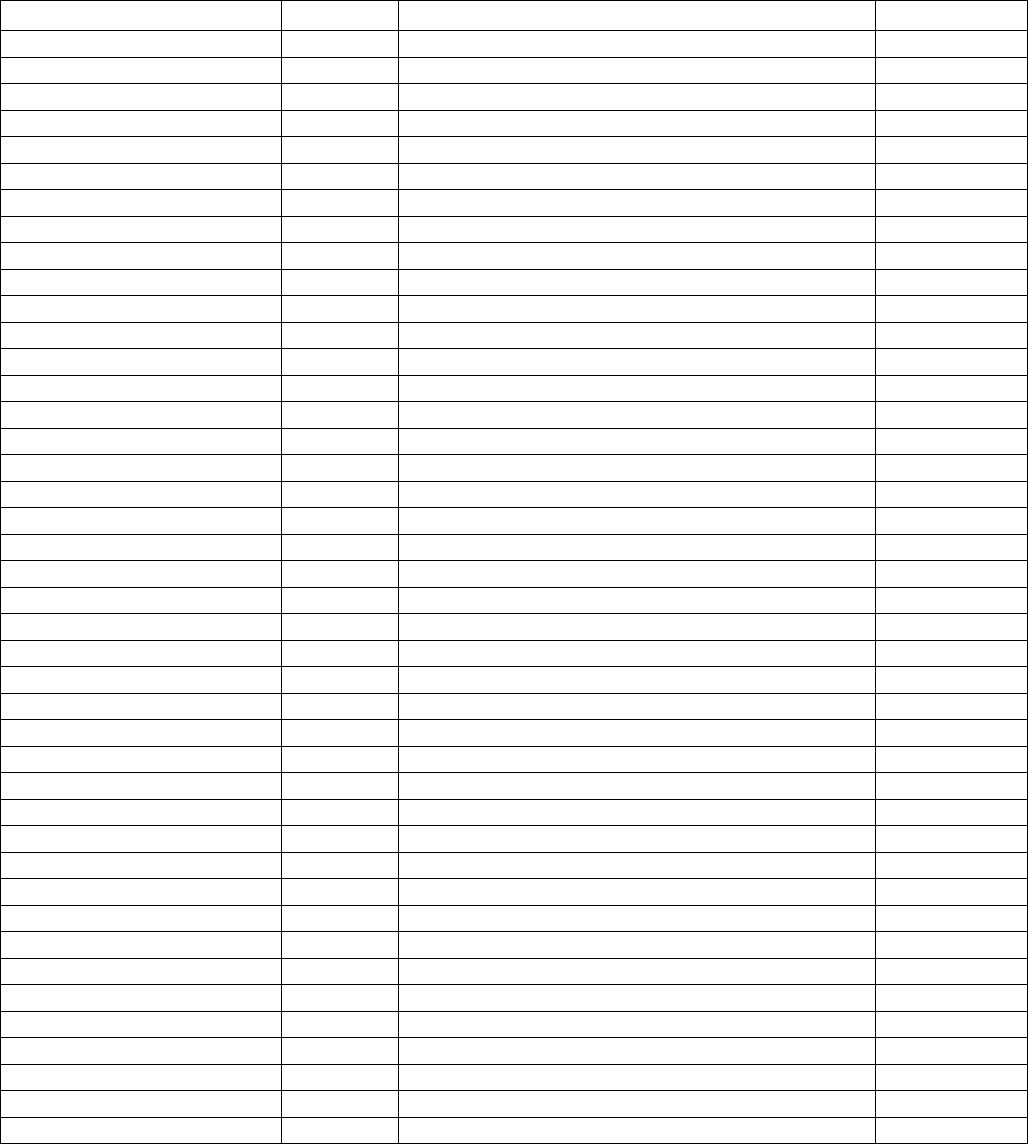

AppendixD

–

CPLDPinout

CPLDPinout

Net Pin Description Direction

50MHZ_CLOCK K2

50MHzClockIn+/‐ 50ppm I

CPLD_TDI J10

CPLDJTAGTDI O

ETHER_TDI A6

EthernetJTAGTDI O

F\L\A\S\H\_\B\Y\T\E\ K7

8/16BitModeSelect O

F\L\A\S\H\_\O\E\ A8

OutputEnable O

F\L\A\S\H\_\R\E\S\E\T\ A2

FlashReset O

F\L\A\S\H\_\W\E\ A3

FlashWriteEnable O

F\L\A\S\H\_\W\P\ A4

FlashWriteProtect O

F\L\A\S\H\_C\E\ A9

FlashChipEnable O

F\P\G\A\_\P\R\O\G\ A5

FPGAAsynchronousReset O

FLASH_A0 K8

Address1[8BitMode] O

FLASH_A1 K1

Address2 I/O

FLASH_A2 H1

Address3 I/O

FLASH_A3 F1

Address4 I/O

FLASH_A4 K4

Address5 I/O

FLASH_A5 C3

Address6 I/O

FLASH_A6 G3

Address7 I/O

FLASH_A7 H3

Address8 I/O

FLASH_A8 A7

Address9 I/O

FLASH_A9 J1

Address10 I/O

FLASH_A10 H10

Address11 I/O

FLASH_A11 G1

Address12 I/O

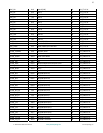

FLASH_A12 D1

Address13 I/O

FLASH_A13 C1

Address14 I/O

FLASH_A14 K5

Address15 I/O

FLASH_A15 E1

Address16 I/O

FLASH_A16 A1

Address17 I/O

FLASH_A17 B1

Address18 I/O

FLASH_A18 A10

Address19 I/O

FLASH_A19 E3

Address20 I/O

FLASH_A20 F3

Address21 I/O

FLASH_A21 C5

Address22 I/O

FLASH_A22 B10

Address23 I/O

FLASH_A23 C4

Address24 I/O

FLASH_A24 D8

Address25 I/O

FLASH_A25 C8

Address26 I/O

FLASH_D15 G10

Address0* I/O

FPGA_CCLK F10

FPGAConfigurationClock O

FPGA_DONE D10

FPGADoneProgramming I

FPGA_INIT E10

FPGAReadytoProgram I/O

LOAD K6

LoadImageRequest I

PEEKABOO H5

OutputLastAddressBeforeDoneRequest I