2.1 Setting the Base Address

The base address of the QS-100D is set using the two DIP switch packs. When

setting the address selection switches, a switch in the "ON" position specifies that

the corresponding address line must be a logic 0 for the port to be selected.

Similarly, a switch in the "OFF" position forces the corresponding address line to

be a logic 1 for the port to be selected.

A full sixteen bit address decode is implemented to reduce the chance of address

conflicts with other adapters in the system. Each serial port on the QS-100D uses

8 consecutive I/O locations. The four ports reside in a contiguous block of I/O

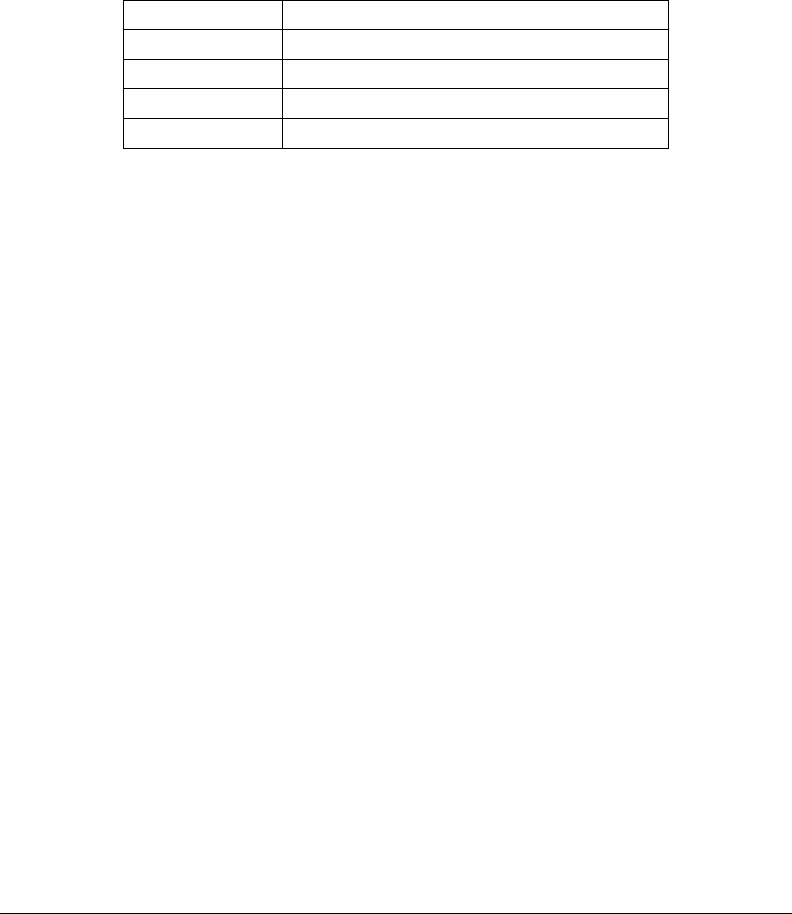

space in eight byte increments, for a total of 32 contiguous bytes, as shown in

Figure 4.

Base Address + 24 to Base Address + 31Serial 4

Base Address + 16 to Base Address + 23Serial 3

Base Address + 8 to Base Address + 15Serial 2

Base Address + 0 to Base Address + 7Serial 1

ADDRESS RANGEPORT

Figure 4 --- Port Address Map

Switches SW1 and SW2 select address lines A15 through A5. The remaining

address lines (A4, A3, A2, A1 and A0) are used by the UART to select the

register being accessed. The sixth position on SW2 is used to enable or disable

the interrupt status register( See Figure 8).

Figure 5 shows how the switches on the QS-100D represent the address values for

serial ports. This figure can be used to explain the examples shown in Figure 5.

2-2 Quatech Inc.