The QS-100D signals a hardware interrupt when any port requires service. The

interrupt signal is maintained until no port requires service. Because the ISA bus

is edge-sensitive, this behavior forces the interrupt service routine to ensure that

all ports are checked before exiting. A way to do this is to poll each port until an

interrupting port is found. After servicing the port, all ports should be checked

again. If any interrupting port is left unserviced the QS-100D will be unable to

signal any further interrupts.

2.4 Interrupt Status Register

The QS-100D is equipped with an interrupt status register which can be used to

simplify the servicing of shared interrupts. If this feature is enabled, the interrupt

status register is accessed in place of the scratchpad of any given UART at base

address + 7. Virtually no commercially available software makes use of the

scratchpad register. The interrupt status register is read-only. The choice of using

the interrupt status register or the UART scratchpads (factory default) is made

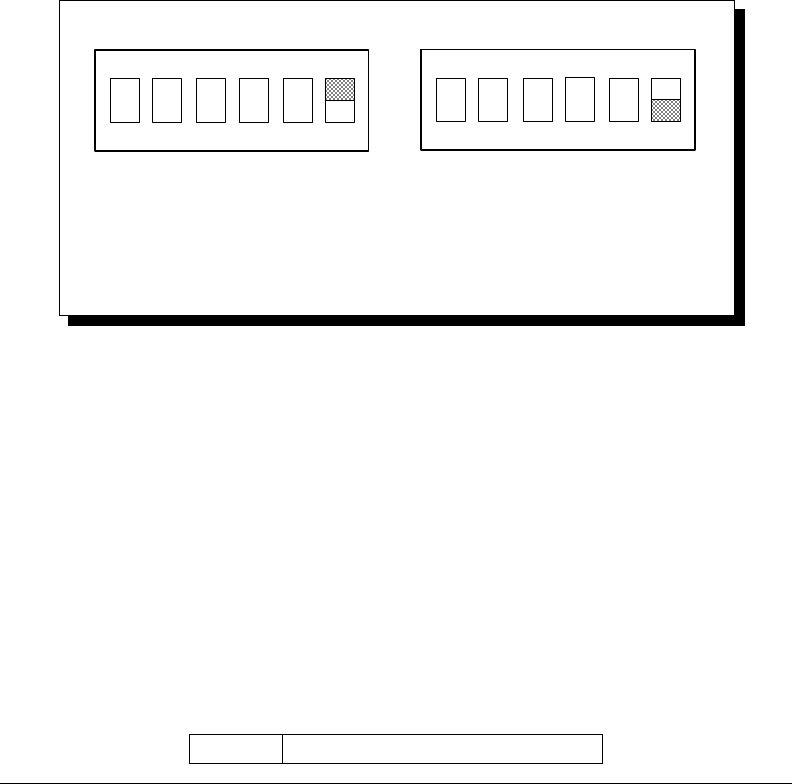

using position 6 of switch SW2 as shown in Figure 8.

ON

123456

SW2

ON

123456

SW2

Slide position 6 of SW2 toward the top of the QS-100D to enable the

interrupt status register, or toward the bottom of the QS-100D to disable it.

Scratchpad Register

(factory default)

Interrupt Status Register

Figure 8--- Enabling the Interrupt Status Register

When a hardware interrupt occurs, reading the interrupt status register will return

the interrupt status of the entire QS-100D, as shown in Figure 9. Individual bits

are cleared as the interrupting ports are serviced. The interrupt service routine

must ensure that the interrupt status register reads zero before exiting, or the

QS-100D will be unable to signal subsequent interrupts.

If the QS-100D is of revision level 'C' or higher, an I/O write to the interrupt

status register will cause another hardware interrupt to be generated if the

interrupt status register is non-zero. The value written is ignored and has no effect

on the contents of the interrupt status register. Software written to take advantage

of this retriggering will be transparent to an older revision of the QS-100D.

DESCRIPTIONBIT

QS-100D User's Manual 2-5