Rev.1.10 Jul 01, 2005 page 88 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 11. DMAC

Under development

This document is under development and its contents are subject to change.

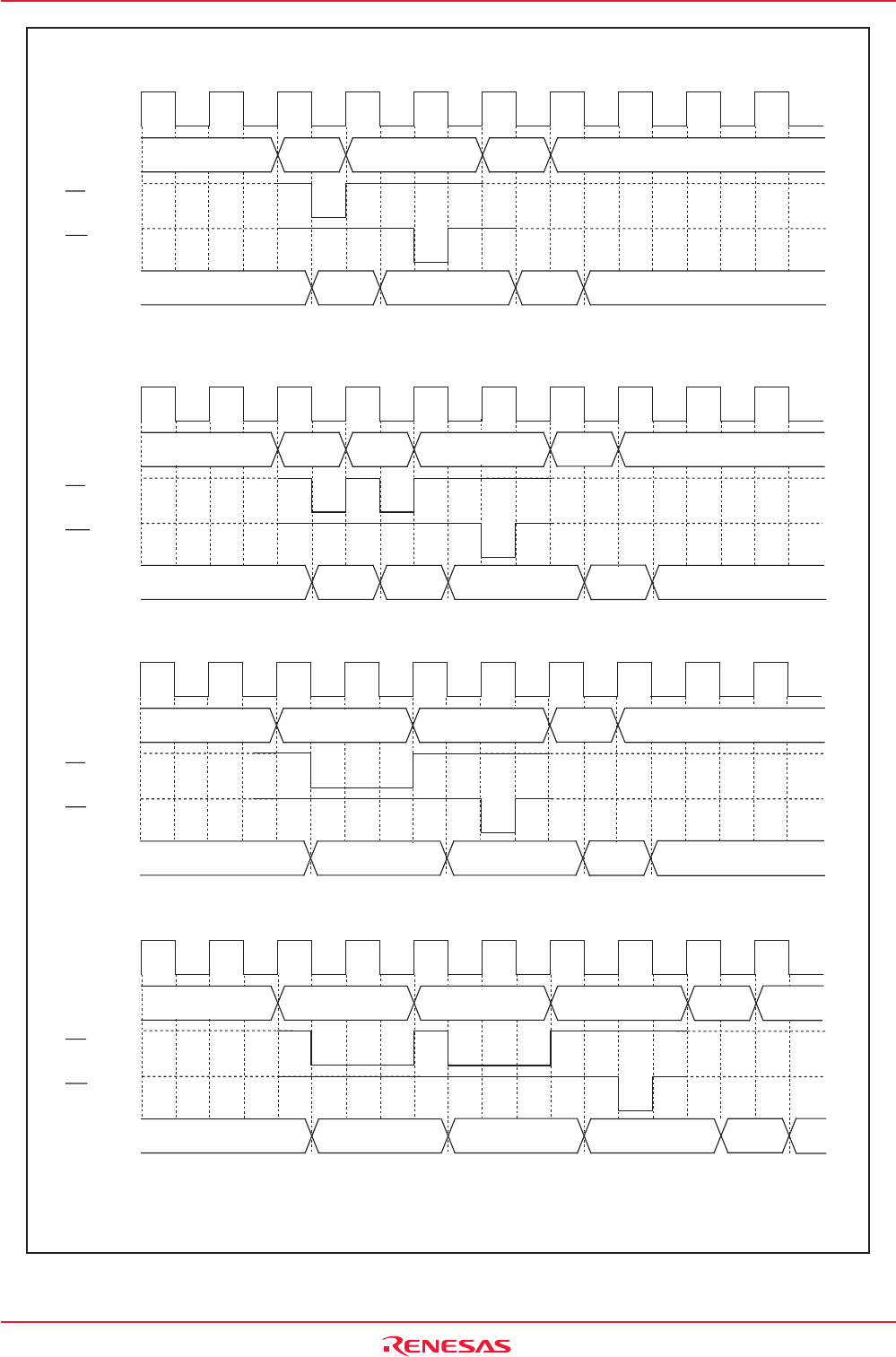

Figure 11.5 Transfer Cycles for Source Read

NOTE:

1. The same timing changes occur with the respective conditions at the destination as at the source.

(1) When the transfer unit is 8 or 16 bits and the source of transfer is an even address

BCLK

Address

bus

RD signal

WR signal

Data

bus

CPU use

CPU use CPU use

CPU useSource

Source

Destination

Destination

Dummy

cycle

Dummy

cycle

(2) When the transfer unit is 16 bits and the source address of transfer is an odd address, or when the

transfer unit is 16 bits and an 8-bit bus is used

BCLK

Address

bus

RD signal

WR signal

Data

bus

CPU use

CPU use CPU use

CPU useSource

Source

Destination

Destination

Dummy

cycle

Dummy

cycle

Source + 1

Source + 1

(3) When the source read cycle under condition (1) has one wait state inserted

BCLK

Address

bus

RD signal

WR signal

Data

bus

CPU use

CPU use CPU use

CPU use

Source

Source

Destination

Destination

Dummy

cycle

Dummy

cycle

(4) When the source read cycle under condition (2) has one wait state inserted

BCLK

Address

bus

RD signal

WR signal

Data

bus

CPU use

CPU use CPU use

CPU useSource

Source

Destination

Destination

Dummy

cycle

Dummy

cycle

Source + 1

Source + 1