Rev.1.10 Jul 01, 2005 page 116 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 12. Timers

Under development

This document is under development and its contents are subject to change.

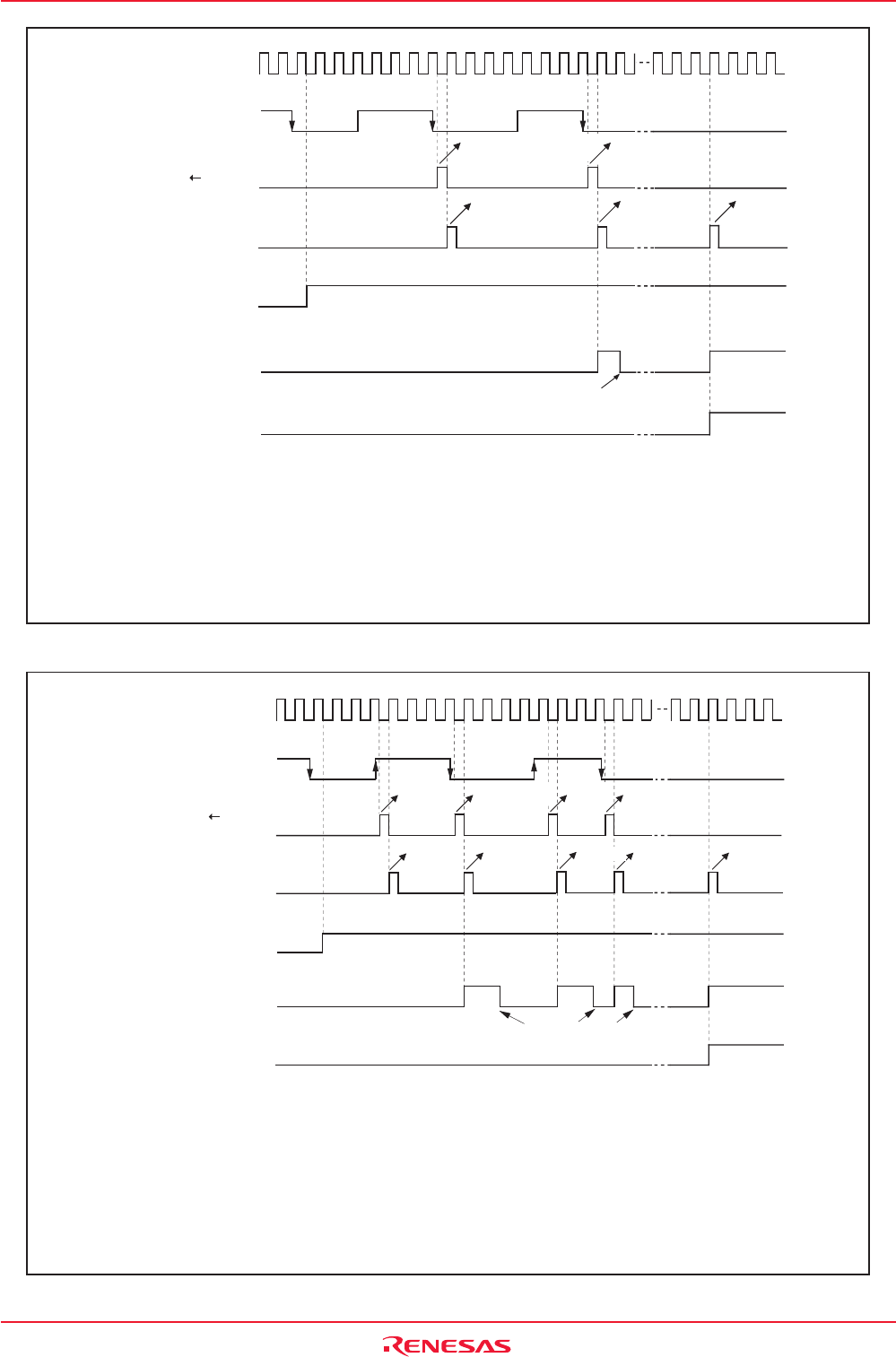

Figure 12.22 Operation Timing When Measuring Pulse Width

Figure 12.21 Operation Timing When Measuring Pulse Period

Count source

Measurement pulse

TBiS bit

IR bit in

TBiIC register

Timing at which counter

reaches "0000h"

"H"

"1"

Transfer

(indeterminate value)

"L"

"0"

"0"

MR3 bit in

TBiMR register

"1"

"0"

i = 0 to 5

NOTES:

1. Counter is initialized at completion of measurement.

2. Timer has overflown.

3. This timing diagram is for the case where the MR1 to MR0 bits in the TBiMR register are "00b" (measure the interval

from falling edge to falling edge of the measurement pulse).

(NOTE 1)(NOTE 1)

(NOTE 2)

Transfer

(measured value)

"1"

Reload register counter

transfer timing

The TB0S to TB2S bits are assigned to bit 5 to bit 7 in the TABSR register, and the TB3S to TB5S bits

are assigned to bit 5 to bit 7 in the TBSR register.

Set to "0" upon accepting an interrupt request or by writing in program

Measurement pulse

"H"

Count source

Timing at which counter

reaches "0000h"

"1"

"1"

Transfer

(measured value)

Transfer

(measured value)

"L"

"0"

"0"

"1"

"0"

(NOTE 1)(NOTE 1)(NOTE 1)

Transfer

(measured

value)

(NOTE 1)

(NOTE 2)

Transfer

(indeterminate

value)

Reload register counter

transfer timing

TBiS bit

Set to "0" upon accepting an interrupt request or by

writing in program

i = 0 to 5

NOTES:

1. Counter is initialized at completion of measurement.

2. Timer has overflown.

3. This timing diagram is for the case where the MR1 to MR0 bits in the TBiMR register are "10b" (measure the

interval from a falling edge to the next rising edge and the interval from a rising edge to the next falling edge

of the measurement pulse).

The TB0S to TB2S bits are assigned to bit 5 to bit 7 in the TABSR register, and the TB3S to TB5S bits

are assigned to bit 5 to bit 7 in the TBSR register.

MR3 bit in

TBiMR register

IR bit in

TBiIC register