Rev.1.10 Jul 01, 2005 page 77 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 9. Interrupt

Under development

This document is under development and its contents are subject to change.

______

9.7 NMI Interrupt

_______ _______ ______

An NMI interrupt request is generated when input on the NMI pin changes state from high to low. The NMI

interrupt is a non-maskable interrupt.

_______

The input level of this NMI interrupt input pin can be read by accessing the P8_5 bit in the P8 register.

This pin cannot be used as an input port.

9.8 Key Input Interrupt

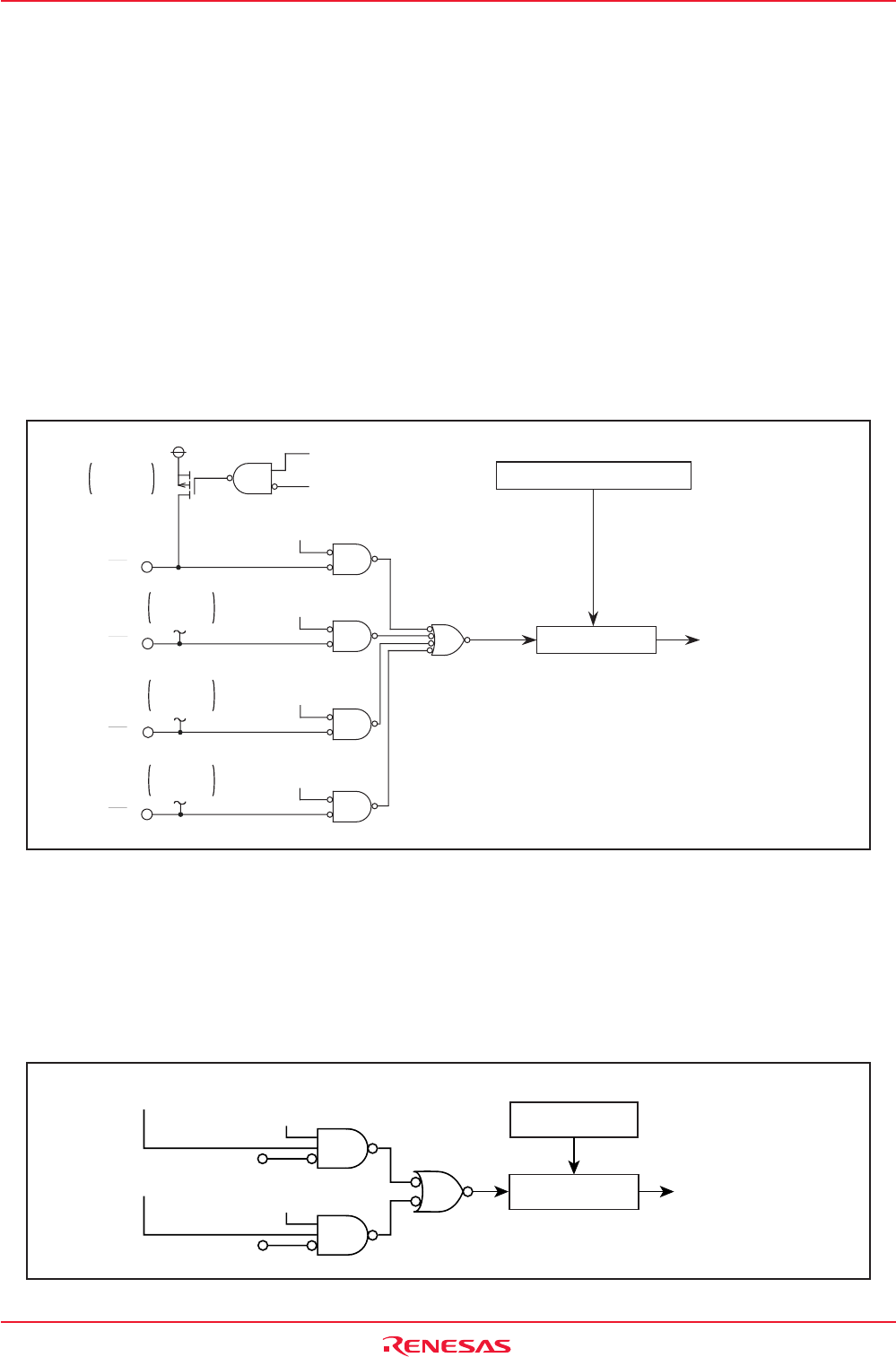

Of P10_4 to P10_7, a key input interrupt request is generated when input on any of the P10_4 to P10_7

pins which has had the PD10_4 to PD10_7 bits in the PD10 register set to “0” (input) goes low. Key input

interrupts can be used as a key-on wake up function, the function which gets the microcomputer out of wait

or stop mode. However, if you intend to use the key input interrupt, do not use P10_4 to P10_7 as analog

input ports. Figure 9.14 shows the block diagram of the key input interrupt. Note, however, that while input

on any pin which has had the PD10_4 to PD10_7 bits set to “0” (input mode) is pulled low, inputs on all other

pins of the port are not detected as interrupts.

Interrupt control circuit

KUPIC register

Key input interrupt

request

KI3

KI2

KI1

KI0

PU25 bit in PUR2 register

PD10_7 bit in PD10 register

Pull-up

transistor

PD10_7 bit in PD10 register

PD10_6 bit in

PD10 register

PD10_5 bit in

PD10 register

PD10_4 bit in

PD10 register

Pull-up

transistor

Pull-up

transistor

Pull-up

transistor

Figure 9.14 Key Input Interrupt Block Diagram

9.9 CAN0/1 Wake-up Interrupt

CAN0/1 wake-up interrupt request is generated when a falling edge is input to CRX0 or CRX1. One interrupt

is allocated to CAN0/1. The CAN0/1 wake-up interrupt is enabled only when the PortEn bit = 1 (CTX/CRX

function) and Sleep bit = 1 (Sleep mode enabled) in the CiCTLR register (i = 0, 1). Figure 9.15 shows the

block diagram of the CAN0/1 wake-up interrupt. Please note that the wake-up message will be lost.

Figure 9.15 CAN0/1 Wake-up Interrupt Block Diagram

CRX1

Interrupt control

circuit

C01WKIC register

PortEn bit in C0CTLR register

PortEn bit in C1CTLR register

Sleep bit in C0CTLR register

Sleep bit in C1CTLR register

CRX0

CAN0/1 wake-up

interrupt request