SH7211 Group

Data Transfer between On-chip RAM Areas with DMAC (Cycle-Stealing Mode)

REJ06B0732-0100/Rev.1.00 March 2008 Page 3 of 13

2. Description of Sample Application

In this sample application, the direct memory access controller (DMAC) is set to auto request mode to transfer 512-

Kbtyte data stored in the on-chip RAM to another address.

2.1 Operation of Modules Used

When a DMA transfer request is made, the DMAC starts to transfer data in accordance with the priority order of

channels and continues the transfer operation until the transfer end condition is met. Transfer requests for the DMAC

are of three kinds: auto requests, external requests, and on-chip peripheral module requests. The bus mode is selectable

as burst mode or cycle-stealing mode.

For details on the DMAC, refer to the section on the direct memory access controller in the SH7211 Group Hardware

Manual.

An overview of the DMAC is given in table 1. Examples of DMA transfer in cycle-stealing mode and burst mode are

shown in figures 1 and 2, respectively. In addition, a block diagram of the DMAC is shown in figure 3.

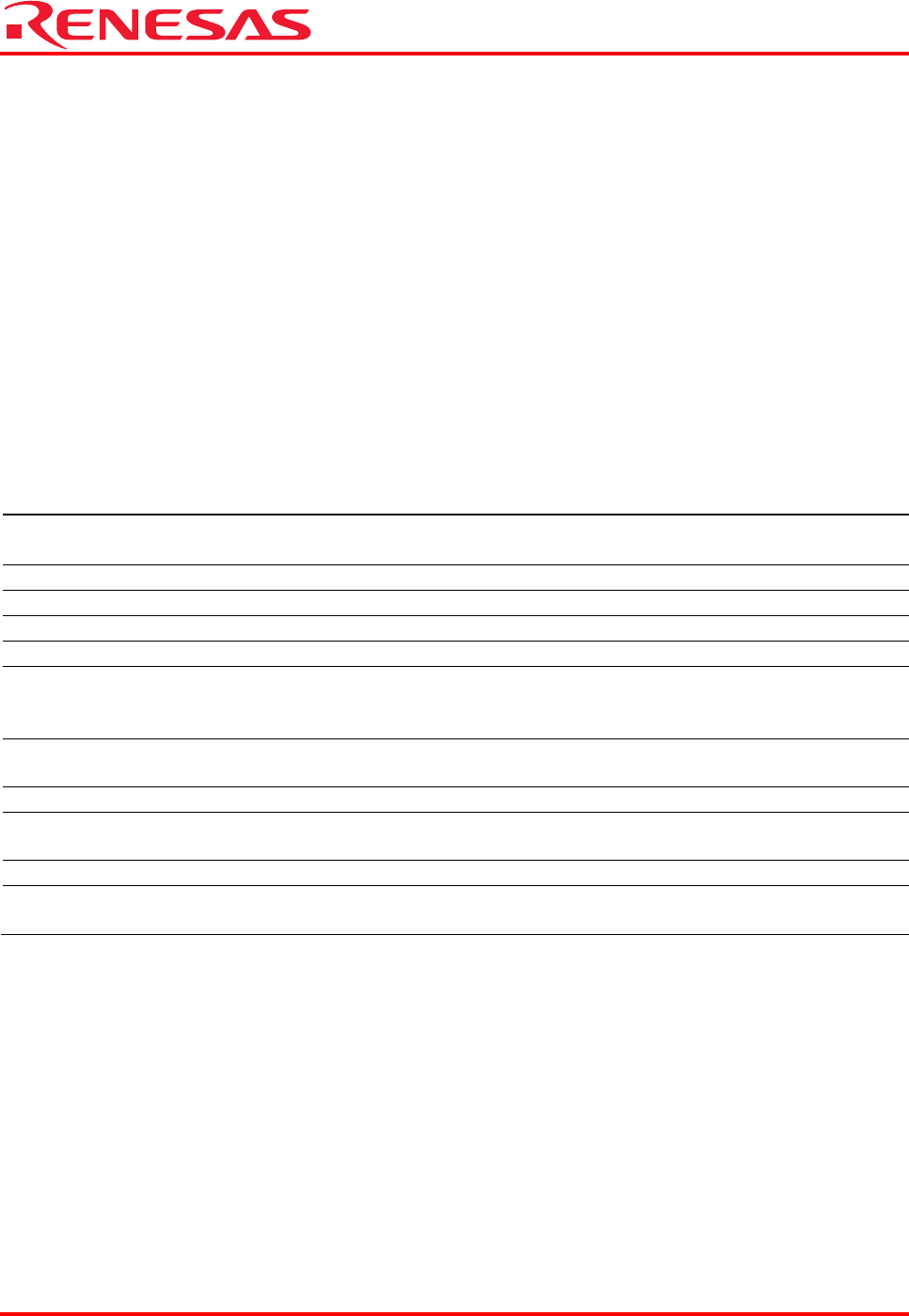

Table 1 Overview of DMAC

Item Description

Number of channels 8 (CH0 to CH7)

Only 4 (CH0 to CH3) can receive external requests.

Address space 4 Gbytes

Length of transfer data Byte, word (2 bytes), longword (4 bytes), and 16 bytes (longword × 4)

Maximum transfer count 16,777,216 (24 bits) transfers

Address mode Single address mode and dual address mode

Transfer request External request, on-chip peripheral module request, and auto request

(SCIF: 8 sources, IIC3: two sources, A/D converter: one source, MTU2:

five sources, CMT: two sources)

Bus mode

Cycle-stealing mode (normal mode and intermittent mode) and burst

mode

Priority level Channel priority fixed mode and round-robin mode

Interrupt request

An interrupt request to the CPU is made when half or all of a transfer

process is completed.

External request detection DREQ input low/high level detection, rising/falling edge detection

Transfer request acknowledge

signal/transfer end signal

Active levels for DACK and TEND can be set independently