SH7211 Group

Data Transfer between On-chip RAM Areas with DMAC (Cycle-Stealing Mode)

REJ06B0732-0100/Rev.1.00 March 2008 Page 6 of 13

2.2 Operational Description of Sample Program

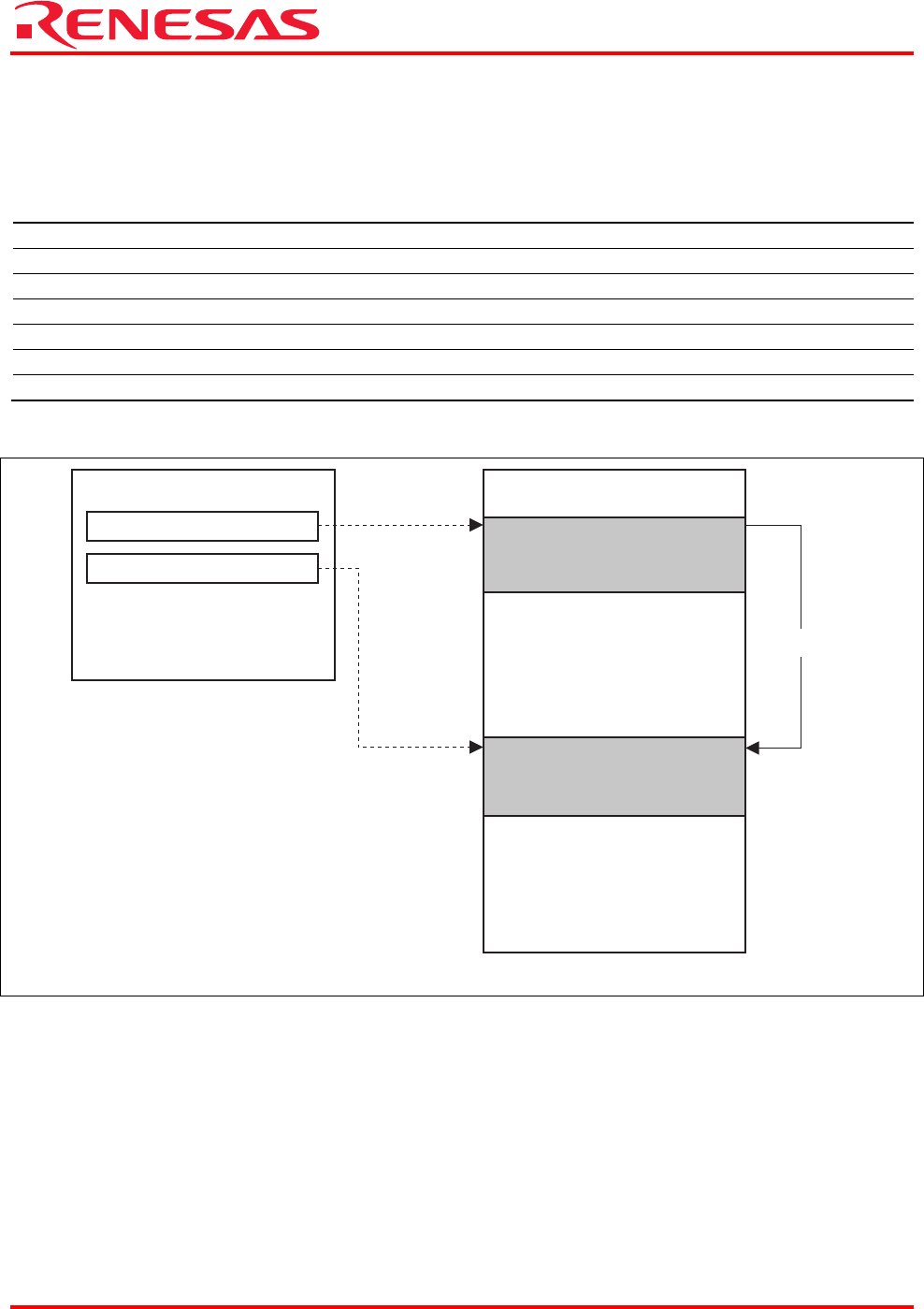

The settings of the DMAC for the sample program are listed in table 4. Also, the operation of the sample program is

illustrated in figure 4.

Table 4 Settings of DMAC

DMA transfer condition Auto request mode

Channel CH0

Length of transfer data 4 bytes

Maximum transfer count 128 transfers (128 × data length of 4 bytes = 512-byte data)

Address mode Dual address mode

Bus mode Cycle-stealing mode

Priority level Channel priority level fixed mode

Interrupt request Disable an interrupt request to the CPU at the end of a transfer

DMAC

H'0xFFF81000

H'0xFFF82000

DAR

SAR

Transfer source

address

On-chip RAM

DMA transfer

512-byte data

512-byte data

Transfer

destination

address

[Legend]

SAR:Source address register

DAR:Destination address register

Figure 4 Operation of Sample Program