SH7211 Group

Data Transfer between On-chip RAM Areas with DMAC (Cycle-Stealing Mode)

REJ06B0732-0100/Rev.1.00 March 2008 Page 4 of 13

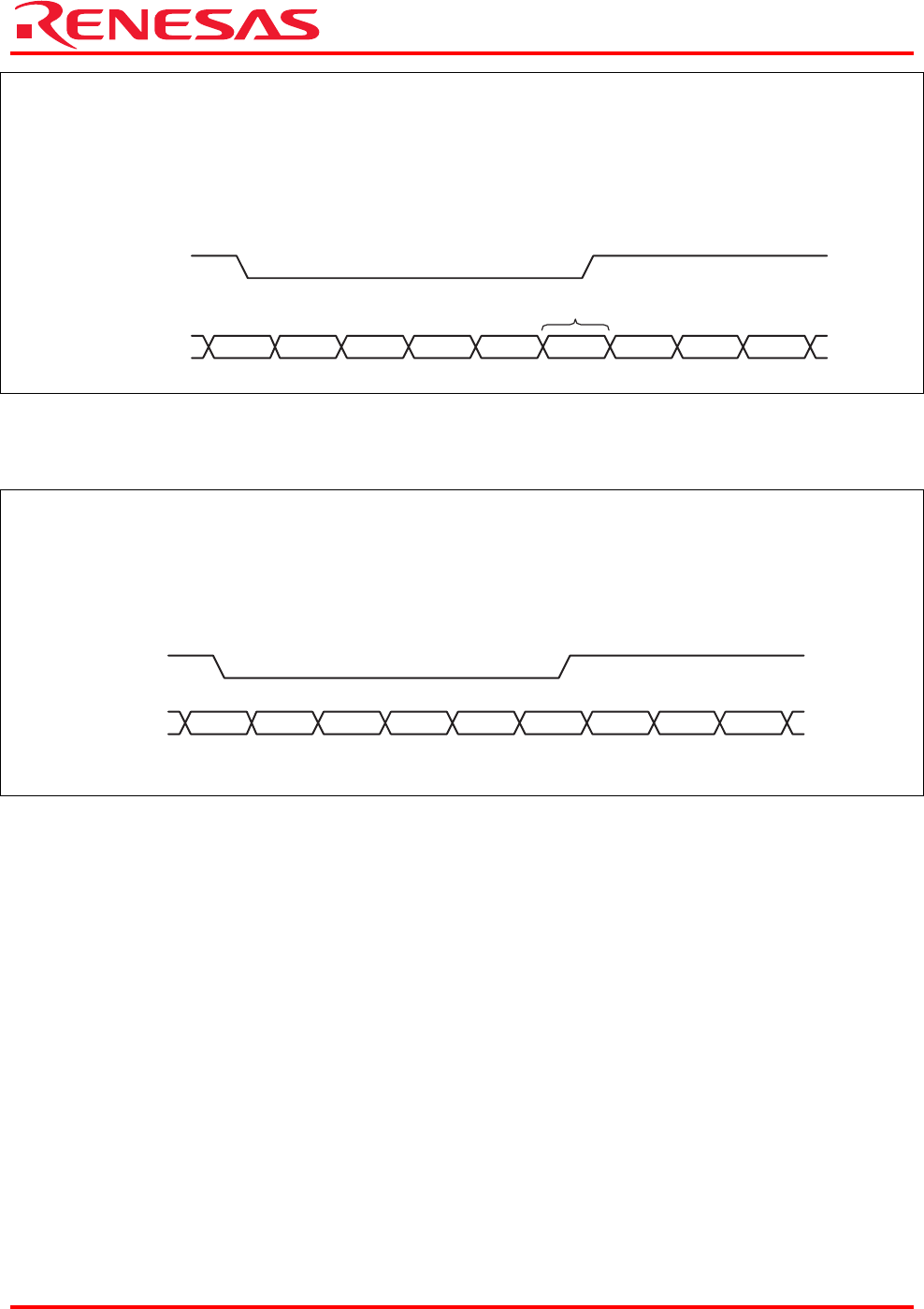

DREQ

Bus mastership returned to CPU once

Bus cycle

WriteRead WriteRead

CPU CPU CPU DMAC DMAC DMAC DMAC CPUCPU

In the normal mode of cycle stealing, bus mastership is given to another bus master after each DMA

transfer of one transfer unit (byte, word, longword, or 16-byte unit). When a subsequent transfer

request occurs, bus mastership is obtained from the other bus master and transfer proceeds for one

transfer unit. When that transfer ends, the bus mastership is passed to another bus master. This is

repeated until the transfer end condition is satisfied.

The cycle-stealing normal mode can be used in transfer across any interval, regardless of the

requesting source, source, and destination of the transfer.

Figure 1 DMA Transfer Example in Cycle-Stealing Normal Mode

(Dual Address, DREQ Low Level Detection)

DREQ

CPU CPU CPU

DMAC DMAC DMAC DMAC CPUCPU

Bus cycle

Read Write Read Write

In burst mode, once the DMAC has obtained bus mastership, it continues to perform transfer without

releasing the bus until the transfer end condition is satisfied. In external mode, however, when the DREQ

signal is being level-detected and changes to the non-active level, even if the tranfer end condition has not

been satisfied, bus mastership is passed to another bus master on completion of the DMA transfer request

for which the request has already been accepted.

Figure 2 DMA Transfer Example in Burst Mode (Dual Address, DREQ Low Level Detection)