samsung.com/semi/sram

20

1H 2011

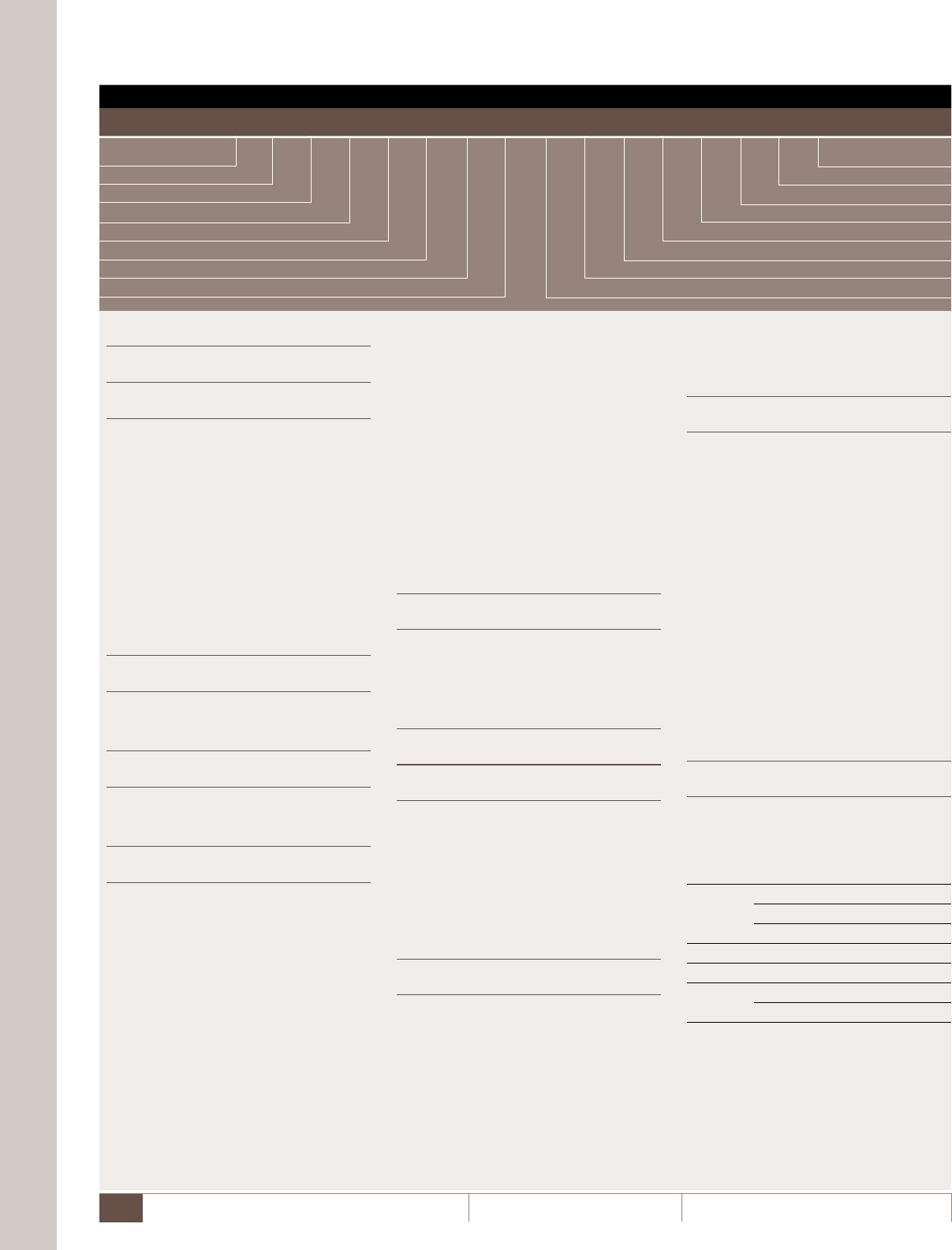

SRAM Ordering Information

1. Memory (K)

2. Sync SRAM: 7

3. Small Classification

A: Sync Pipelined Burst

B: Sync Burst

D: Double Data Rate

I: Double Data Rate II, Common I/O

J: Double Data Rate, Separate I/O

K: Double Data II+, Common I/O

M: Sync Burst + NtRAM

N: Sync Pipelined Burst + NtRAM

P: Sync Pipe

Q: Quad Data Rate I

R: Quad Data Rate II

S: Quad Data Rate II+

4~5. Density

80: 8M 16: 18M

40: 4M 32: 36M

64: 72M

6~7. Organization

08: x8 09: x9

18: x18 32: x32

36: x36

8~9. Vcc, Interface, Mode

00: 3.3V,LVTTL,2E1D WIDE

01: 3.3V,LVTTL,2E2D WIDE

08: 3.3V,LVTTL,2E2D Hi SPEED

09: 3.3V,LVTTL,Hi SPEED

11: 3.3V,HSTL,R-R

12: 3.3V,HSTL,R-L

14: 3.3V,HSTL,R-R Fixed ZQ

22: 3.3V,LVTTL,R-R

23: 3.3V,LVTTL,R-L

25: 3.3V,LVTTL,SB-FT WIDE

30: 1.8/2.5/3.3V,LVTTL,2E1D

31: 1.8/2.5/3.3V,LVTTL,2E2D

35: 1.8/2.5/3.3V,LVTTL,SB-FT

44: 2.5V,LVTTL,2E1D

45: 2.5V,LVTTL,2E2D

49: 2.5V,LVTTL,Hi SPEED

52: 2.5V,1.5/1.8V,HSTL,Burst2

54: 2.5V,1.5/1.8V,HSTL,Burst4

62: 2.5V/1.8V,HSTL,Burst2

64: 2.5V/1.8V,HSTL,Burst4

66: 2.5V,HSTL,R-R

74: 1.8V,2.5V,HSTL,All

82: 1.8V,HSTL,Burst2

84: 1.8V,HSTL,Burst4

88: 1.8V,HSTL,R-R

T2: 1.8V,2Clock Latency,Burst2

T4: 1.8V,2Clock Latency,Burst4

U2: 1.8V,2.5Clock Latency,Burst2

U4: 1.8V,2.5Clock Latency,Burst4

10. Generation

M: 1st Generation

A: 2nd Generation

B: 3rd Generation

C: 4th Generation

D: 5th Generation

11. “--”

12. Package

H: BGA,FCBGA,PBGA

G: BGA, FCBGA, FBGA (LF)

F: FBGA

E: FBGA (LF)

Q: (L)QPF

P: (L)QFP(LF)

C: CHIP BIZ

W: WAFER

13. Temp, Power

COMMON (Temp,Power)

0: NONE,NONE (Containing of error

handling code)

C: Commercial,Normal

E: Extended,Normal

I: Industrial,Normal

WAFER, CHIP BIZ Level Division

0: NONE,NONE

1: Hot DC sort

2: Hot DC, selected AC sort

14~15. Speed

Sync Burst,Sync Burst + NtRAM

< Mode is R-L > (Clock Accesss Time)

65: 6.5ns 70: 7ns

75: 7.5ns 80: 8ns

85: 8.5ns

Other Small Classification (Clock Cycle Time)

10: 100MHz 11: 117MHz

13: 133MHz 14: 138MHz

16: 166MHz 20: 200MHz

25: 250MHz

26: 250MHz(1.75ns) 27: 275MHz

30: 300MHz 33: 333MHz

35: 350MHz 37: 375MHz

40: 400MHz(t-CYCLE) 42: 425MHz

45: 450MHz

50: 500MHz (except Sync Pipe)

16. Packing Type (16 digit)

- Common to all products, except of Mask ROM

- Divided into TAPE & REEL (In Mask ROM,

divided into TRAY, AMMO packing separately)

Type Packing Type New Marking

Component TAPE & REEL T

Other (Tray, Tube, Jar) 0 (Number)

Stack S

Component TRAY Y

(Mask ROM) AMMO PACKING A

Module MODULE TAPE & REEL P

MODULE Other Packing M

SYNCHRONOUS SRAM ORDERING INFORMATION

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

K 7 X X X X X X X X - X X X X X

SAMSUNG Memory

Sync SRAM

Small Classication

Density

Density

Organization

Organization

Vcc, Interface, Mode

Packaging Type

Speed

Speed

Temp, Power

Package

---

Generation

Vcc, Interface, Mode