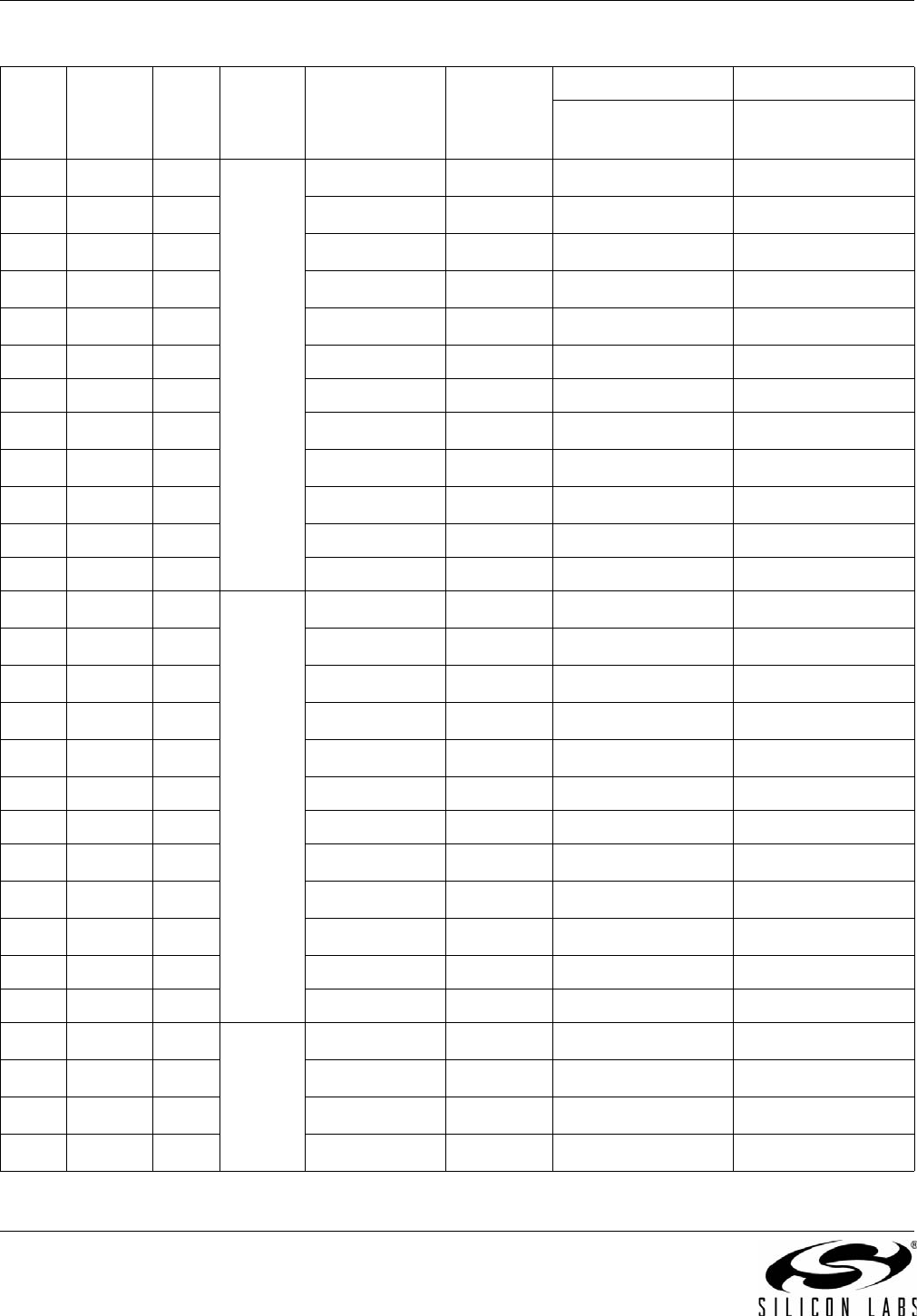

Si53xx-RM

54 Rev. 0.5

28 MLLM

77.76 1/4 19.44 19.44 0.008

29 MLLH

1/2 38.88 38.88 0.008

30 MLML

1 77.76 77.76 0.008

31 MLMM

2 155.52 155.52 0.008

32 MLMH

2 x (255/238) 166.63 166.63 NA

33 MLHL 2 x (255/237) 167.33 167.33 NA

34 MLHM 2 x (255/236) 168.04 168.04 NA

35 MLHH

4 311.04 311.04 0.008

36 MMLL

8 622.08 622.08 0.008

37 MMLM

8 x (255/238) 666.51 666.51 NA

38 MMLH 8 x (255/237) 669.33 669.33 NA

39 MMML 8 x (255/236) 672.16 672.16 NA

40 MMMM

155.52 1/8 19.44 19.44 0.008

41 MMMH

1/4 38.88 38.88 0.008

42 MMHL

1/2 77.76 77.76 0.008

43 MMHM

1 155.52 155.52 0.008

44 MMHH

255/238 166.63 166.63 NA

45 MHLL 255/237 167.33 167.33 NA

46 MHLM 255/236 168.04 168.04 NA

47 MHLH

2 311.04 311.04 0.008

48 MHML

4 622.08 622.08 0.008

49 MHMM

4 x (255/238) 666.51 666.51 NA

50 MHMH 4 x (255/237) 669.33 669.33 NA

51 MHHL 4 x (255/236) 672.16 672.16 NA

52 MHHM

166.63 238/255 155.52 155.52 NA

53 MMHM

1 166.63 166.63 NA

54 MHHH

4 x (238/255) 622.08 622.08 NA

55 MHML

4 666.51 666.51 NA

Table 16. SONET Clock Multiplication Settings (FRQTBL=L) (Continued)

No FRQSEL

[3:0]

WB

f

IN

MHz Mult Factor Nominal

f

OUT

MHz

All Devices Si5366 Only

f

CKOUT5

(MHz)

(CK_CONF = 0)

FS_OUT (MHz)

(CK_CONF = 1)