Si53xx-RM

Rev. 0.5 61

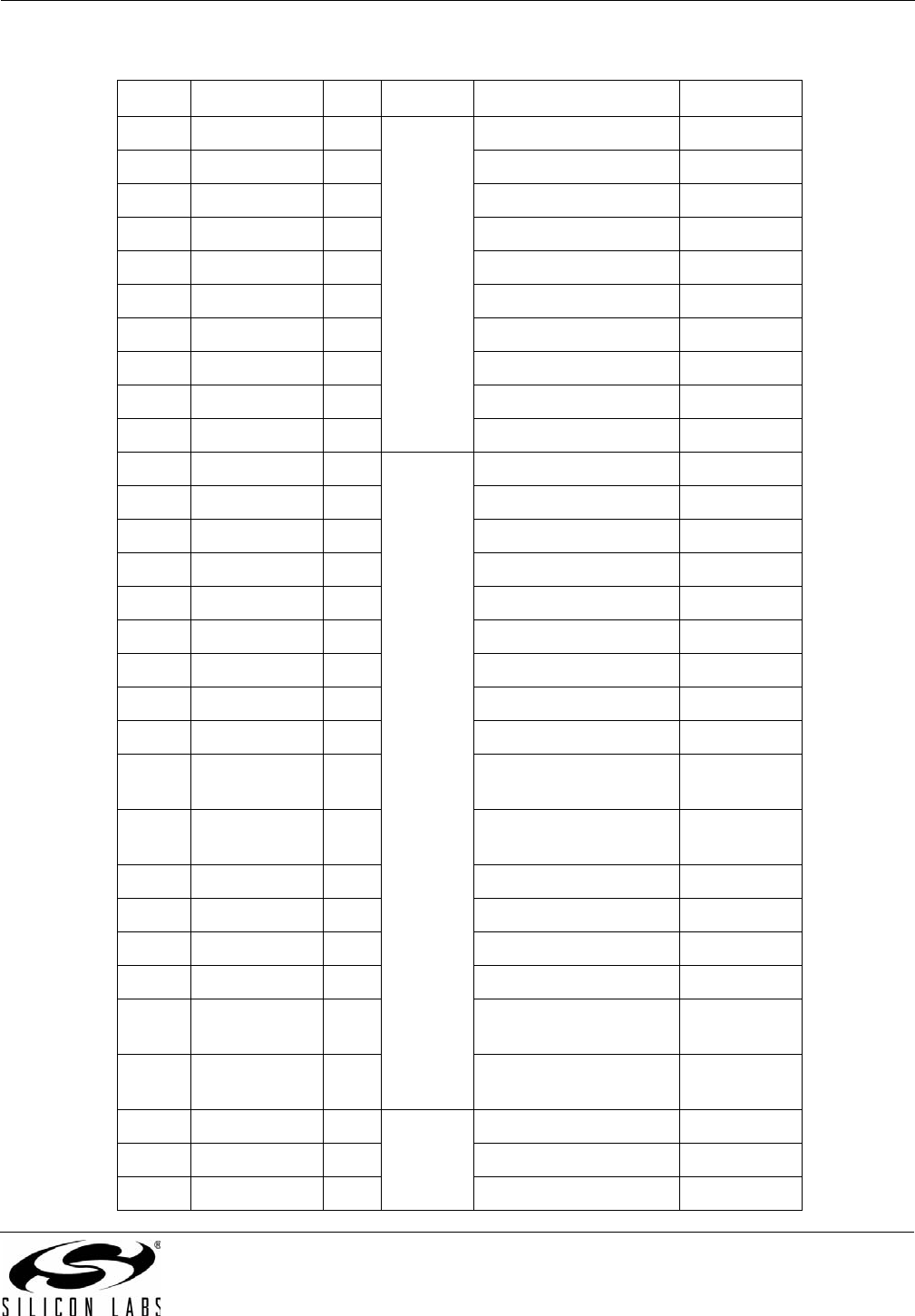

Table 18. SONET to Datacom Clock Multiplication Settings

Setting FRQSEL[3:0]

WB

f

IN

(MHz) Mult Factor f

OUT

* (MHz)

0 LLLL 0.008 3125 25

1 LLLM 6480 51.84

2 LLLH 53125/8 53.125

3 LLML 15625/2 62.5

4 LLMM 53125/4 106.25

5 LLMH 15625 125

6 LLHL 78125/4 156.25

7 LLHM 159375/8 159.375

8 LLHH 53125/2 212.5

9 LMLL 53125 425

10 LMLM 19.440 625/486 25

11 LMLH 10625/3888 53.125

12 LMML 3125/972 62.5

13 LMMM 10625/1944 106.25

14 LMMH 3125/486 125

15 LMHL 15625/1944 156.25

16 LMHM 31875/3888 159.375

17 LMHH 15625/1944 x 66/64 161.13

18 LHLL 31875/3888 x 66/64 164.36

19 LHLM 15625/1944 x 66/

64 x 255/238

172.64

20 LHLH 31875/3888 x 66/

64 x 255/238

176.1

21 LHML 10625/972 212.5

22 LHMM 10625/486 425

23 LHMH 15625/486 x 66/64 644.53

24 LHHL 31875/972 x 66/64 657.42

25 LHHM 15625/486 x 66/

64 x 255/238

690.57

26 LHHH 31875/972 x 66/

64 x 255/238

704.38

27 MLLL 27.000 1 27

28 MLLM 250/91 74.17582

29 MLLH 11/4 74.25