Si53xx-RM

72 Rev. 0.5

6.6.5. Disabling FS_OUT (Si5366)

The FS_OUT maybe disabled via the DBLFS pin, see Table 29. The additional state (M) provided allows for

FS_OUT to drive a CMOS load while the other clock outputs use a different signal format as specified by the

SFOUT[1:0] pins.

6.7. Output Clock Drivers

The devices include a flexible output driver structure that can drive a variety of loads, including LVPECL, LVDS,

CML, and CMOS formats. The signal format is selected jointly for all outputs using the SFOUT [1:0] pins, which

modify the output common mode and differential signal swing. See Table 4, “DC Characteristics” for output driver

specifications. The SFOUT [1:0] pins are three-level input pins, with the states designated as L (ground), M (V

DD

/

2), and H (V

DD

).

Table 30 shows the signal formats based on the supply voltage and the type of load being driven. For the CMOS

setting (SFOUT = LH), both output pins drive single-ended in-phase signals and should be externally shorted

together to obtain the drive strength specified in Table 4, “DC Characteristics”, see Section “8.2. Output Clock

Drivers”.

The SFOUT [1:0] pins can also be used to disable the output. Disabling the output puts the CKOUT+ and CKOUT–

pins in a high-impedance state relative to V

DD

(common mode tri-state) while the two outputs remain connected to

each other through a 200 on-chip resistance (differential impedance of 200 ). The maximum amount of internal

circuitry is powered down, minimizing power consumption and noise generation. Changing SFOUT without a reset

causes the output to output skew to become random. When SFOUT = LH for CMOS, PLL bypass mode is not

supported.

6.7.1. LVPECL and CMOS TQFP Output Signal Format Restrictions at 3.3 V (Si5365, Si5366)

The LVPECL and CMOS output formats draw more current than either LVDS or CML. However, the allowed output

format pin settings are restricted so that the maximum power dissipation for the TQFP devices is limited when they

are operated at 3.3 V. When SFOUT[1:0] = MH or LH (for either LVPECL or CMOS), either DBL5 must be H or

DBL34 must be high.

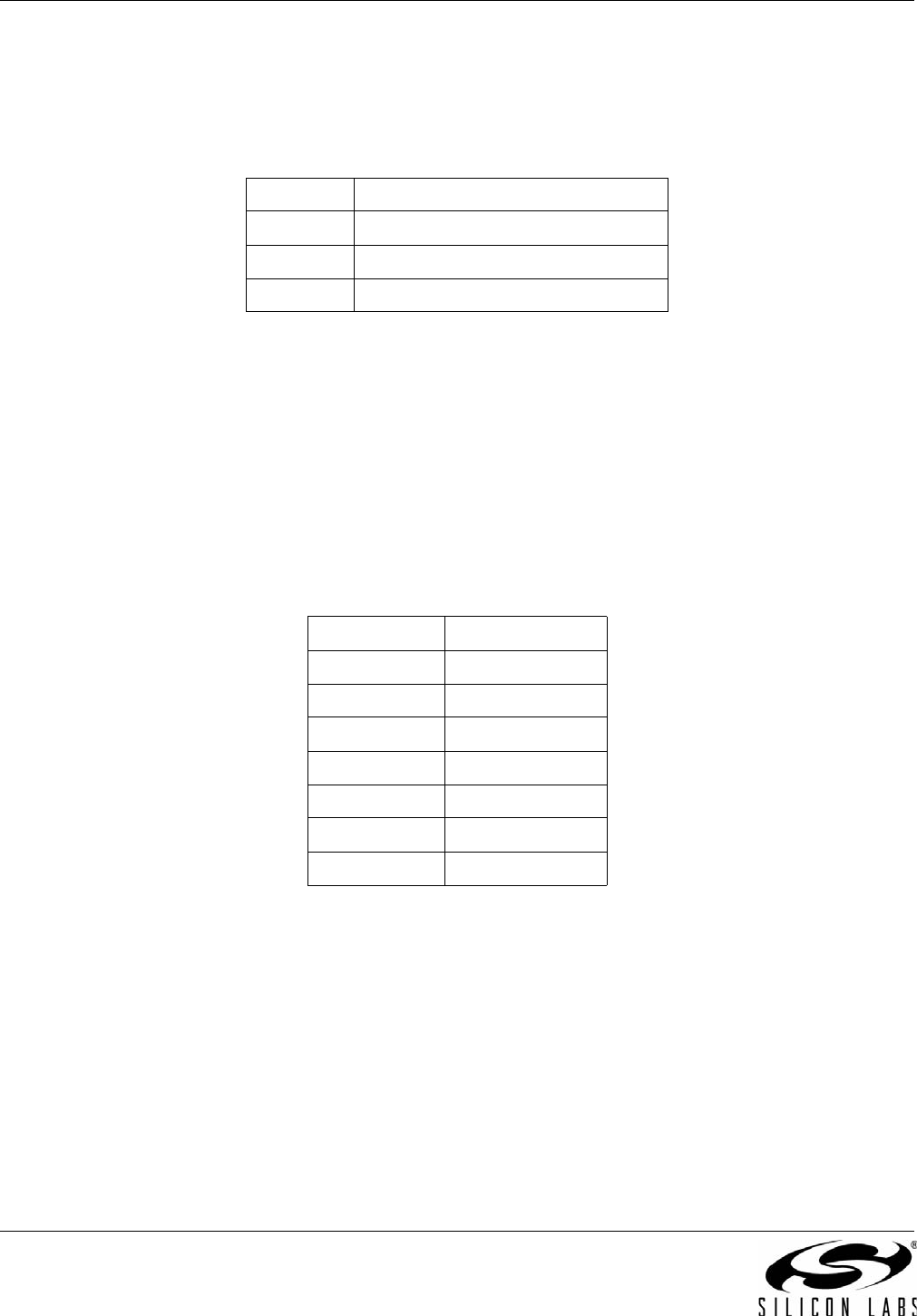

Table 29. FS_OUT Disable Control (DBLFS)

DBLFS FS_OUT State

H Tri-State/Powerdown

M Active/CMOS Format

L Active/SFOUT[1:0] Format

Table 30. Output Signal Format Selection (SFOUT)

SFOUT[1:0] Signal Format

HL CML

HM LVDS

LH CMOS

LM Disabled

MH LVPECL

ML Low-swing LVDS

All Others Reserved