Si53xx-RM

Rev. 0.5 93

The NC5_LS divider uses CKOUT2 as its clock input to derive FS_OUT. The limits for the NC5_LS divider are

NC5_LS = [1, 2, 4, 6, …, 2

19

]

f

CKOUT2

< 710 MHz

Note that when in frame synchronization realignment mode, writes to NC5_LS are controlled by FPW_VALID. See

section “7.8.4. FS_OUT Polarity and Pulse Width Control (Si5368)”.

Common NC5_LS divider settings on FS_OUT are shown in Table 45.

7.8.1. FSYNC Realignment (Si5368)

The FSYNC_ALIGN_PIN bit determines if the realignment will be pin-controlled via the FS_ALIGN pin or register-

controlled via the FSYNC_ALIGN_REG register bit. The active CKIN3 or CKIN4 edge to be used is controlled via

the FSYNC_POL register bit.

In either FSYNC alignment control mode, the resolution of the phase realignment is 1 clock cycle of CKOUT2. If

the realignment control is not active, the NC5 divider will continuously divide down its f

CKOUT2

input. This

guarantees a fixed number of high-frequency clock (CKOUT2) cycles between each FS_OUT cycle.

At power-up, the device automatically performs a realignment of FS_OUT using the currently active sync input.

After this, as long as the PLL remains in lock and a realignment is not requested, FS_OUT will include a fixed

number of high-speed clock cycles, even if input clock switches are performed. If many clock switches are

performed in phase build-out mode, it is possible that the input sync to output sync phase relationship will shift due

to the accumulated residual phase transients of the phase build-out circuitry. The ALIGN_ERR[8:0] status register

reports the deviation of the input-to-output sync phase skew from the desired FSYNC_SKEW[16:0] value in units of

f

CKOUT2

periods. A programmable threshold to trigger the ALIGN_INT alarm can be set via the ALIGN_THR[2:0]

bits, whose settings are given in Table 46. If the sync alignment error exceeds the threshold in either the positive or

negative direction, the alarm becomes active. If it is then desired to reestablish the desired input-to-output sync

phase relationship, a realignment can be performed. A realignment request may cause FS_OUT to

instantaneously shift its output edge location in order to align with the active input sync phase.

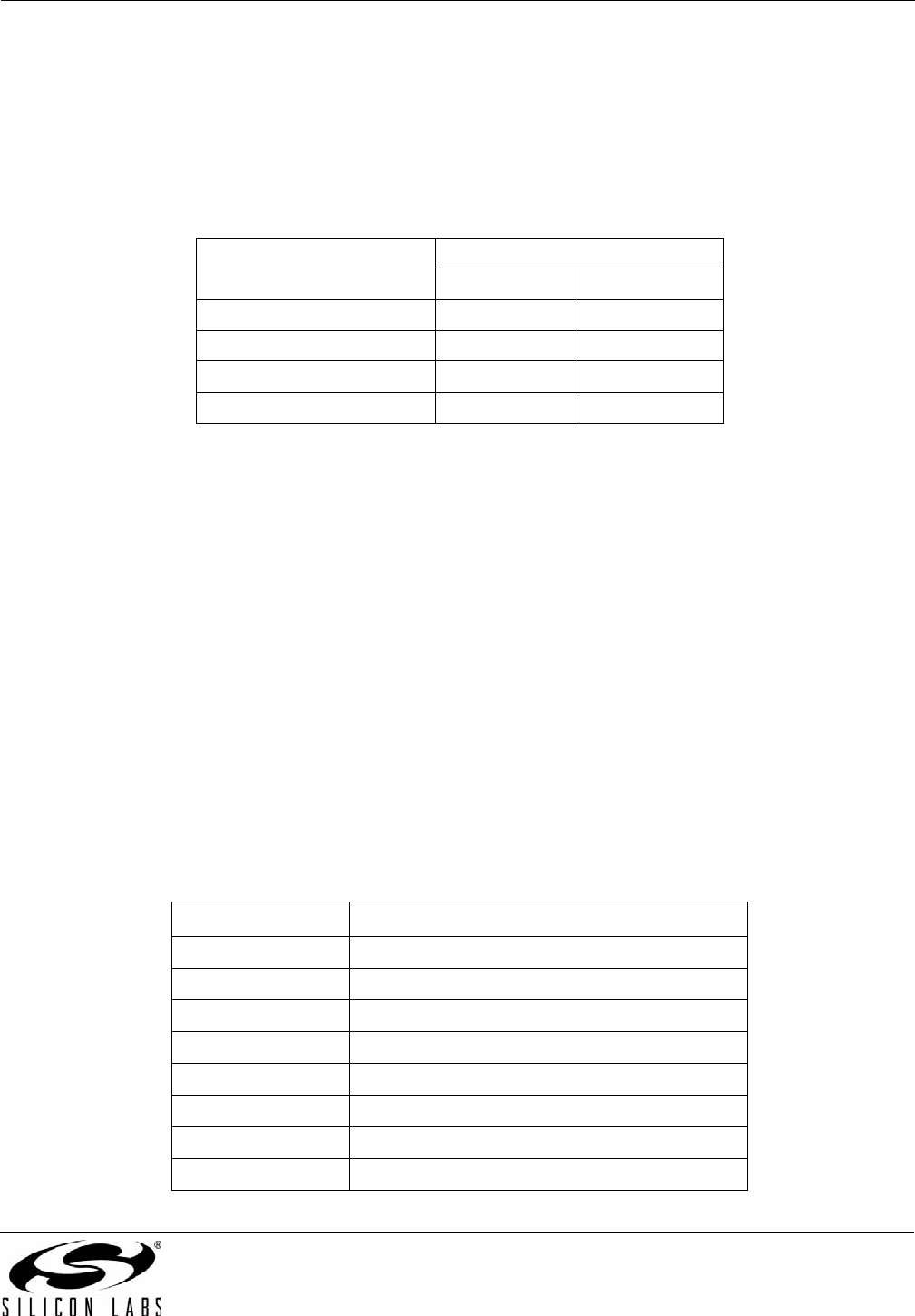

Table 45. Common NC5 Divider Settings

CKOUT2 Frequency (MHz) NC5 Divider Setting

2 kHz FS_OUT 8 kHz FS_OUT

19.44 9720 2430

77.76 38880 9720

155.52 77760 19440

622.08 311040 77760

Table 46. Alignment Alarm Trigger Threshold

ALIGN_THR [2:0] Alarm Trigger Threshold (Units of T

CKOUT2

)

000 4

001 8

010 16

011 32

100 48

101 64

110 96

111 128