Si53xx-RM

58 Rev. 0.5

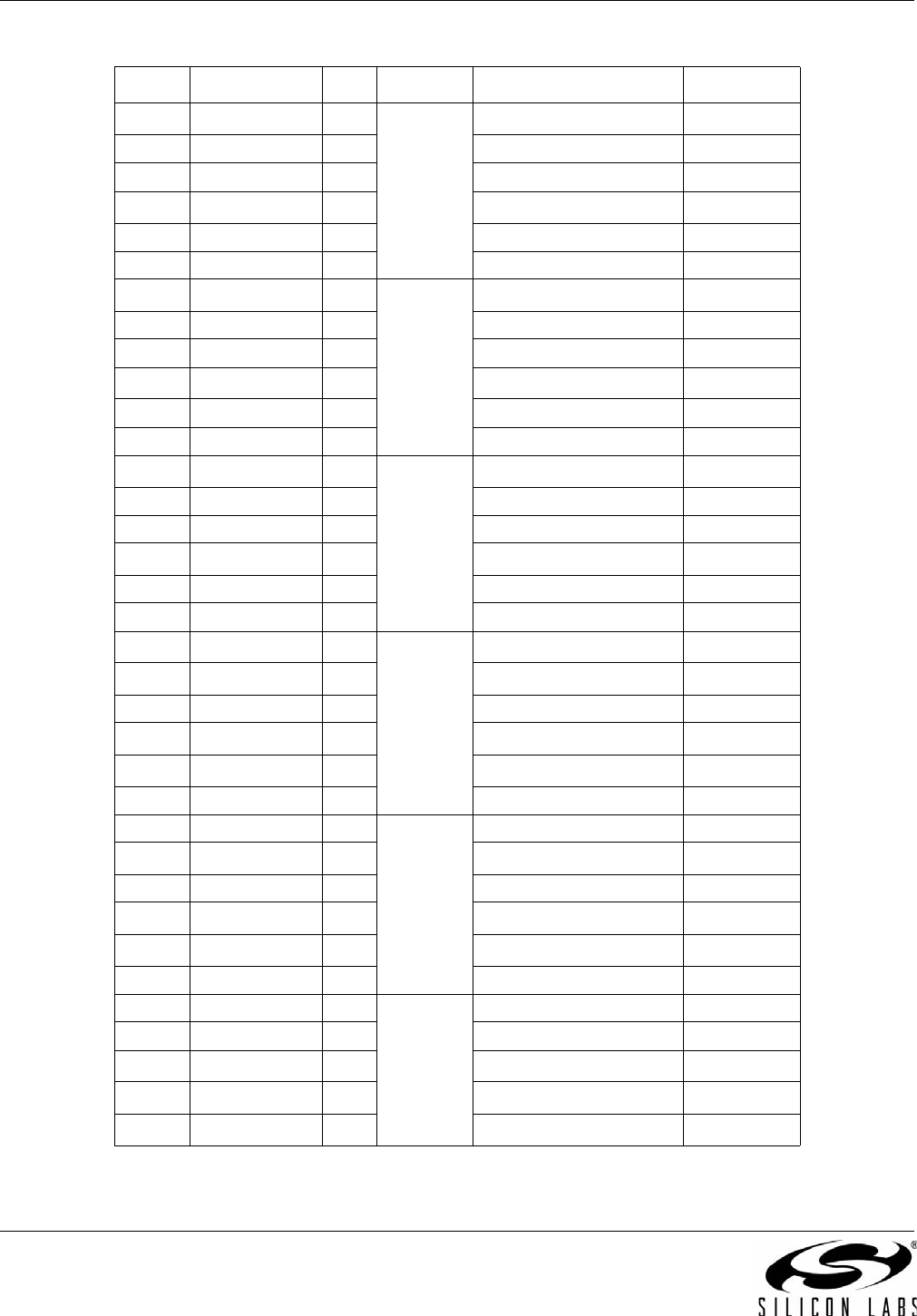

34 MLHM

125 10/8 x 66/64 161.13

35 MLHH 10/8 x 66/64 x 255/238 172.64

36 MMLL 10/8 x 66/64 x 255/237 173.37

37 MMLM

5x66/64 644.53

38 MMLH 5 x 66/64 x 255/238 690.57

39 MMML 5 x 66/64 x 255/237 693.48

40 MMMM

156.25 66/64 161.13

41 MMMH 66/64 x 255/238 172.64

42 MMHL 66/64 x 255/237 173.37

43 MMHM

4x66/64 644.53

44 MMHH 4 x 66/64 x 255/238 690.57

45 MHLL 4 x 66/64 x 255/237 693.48

46 MMMM

159.375 66/64 164.36

47 MMMH 66/64 x 255/238 176.1

48 MMHL 66/64 x 255/237 176.84

49 MMHM

4 x 66/64 657.4

50 MMHH 4 x 66/64 x 255/238 704.38

51 MHLL 4 x 66/64 x 255/237 707.35

52 MHLM

161.13 4/5 x 64/66 125

53 MHLH

255/238 172.64

54 MHML 255/237 173.37

55 MHMM

4644.53

56 MHMH

4 x 255/238 690.57

57 MHHL 4 x 255/237 693.48

58 MHHM 164.36 2/3 x 64/66 106.25

59 MHLH

255/238 176.1

60 MHML 255/237 176.84

61 MHMM

4657.42

62 MHMH

4 x 255/238 704.38

63 MHHL 4 x 255/237 707.35

64 MHHH 172.64 4/5 x 64/66 x 238/255 125

65 HLLL 64/66 x 238/255 156.25

66 HLLM

238/255 161.13

67 HLLH

4 x 238/255 644.53

68 MHMM

4690.57

Table 17. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) (Continued)

Setting FRQSEL[3:0]

WB

f

IN

(MHz) Mult Factor f

OUT

* (MHz)