Si53xx-RM

Rev. 0.5 99

7.11.3. C1B, C2B (Si5319, Si5324, Si5325, Si5326, Si5327, Si5374, Si5375)

A LOS condition causes the associated LOS1_INT or LOS2_INT read only register bit to be set. A LOS condition

on CKIN_1 will also be reflected onto C1B if CK1_BAD_PIN = 1. Likewise, a LOS condition on CKIN_2 will also be

reflected onto C2B if CK2_BAD_PIN =1.

A FOS condition causes the associated FOS1_INT or FOS2_INT read only register bit to be set. FOS monitoring is

enabled or disabled using the FOS_EN bit. If FOS is enabled (FOS_EN = 1) and CK1_BAD_PIN = 1, a FOS

condition will also be reflected onto its associated output pin, C1B or C2B. If FOS is disabled (FOS_EN =0), the

FOS1_INT and FOS2_INT register bits do not affect the C1B and C2B alarm outputs, respectively.

Once an LOS or FOS alarm is asserted on one of the input clocks, it is held high until the input clock is validated

over a designated time period. The validation time is programmable via the VALTIME[1:0] register bits as shown in

Table 48 on page 96. If another error condition on the same input clock is detected during the validation time then

the alarm remains asserted and the validation time starts over.

[Si5326]: Note that hitless switching between input clocks applies only when the input clock validation time

VALTIME[1:0] = 01 or higher.

7.11.4. LOS (Si5319, Si5375)

A LOS condition causes the LOS_INT read only register bit to be set. This LOS condition will also be reflected onto

the INT_CB pin.

7.11.5. C1B, C2B, C3B, ALRMOUT (Si5367, Si5368, Si5369 [CK_CONFIG_REG = 0])

The generation of alarms on the C1B, C2B, C3B, and ALRMOUT outputs is a function of the input clock

configuration, and the frequency offset alarm enable as shown in Table 52. The LOSn_INT and FOSn_INT signals

are the raw outputs of the alarm monitors. These appear directly in the device status registers. Sticky versions of

these bits (LOSn_FLG, FOSn_FLG) drive the output interrupt and can be individually masked. When the device

inputs are configured as four input clocks (CK_CONFIG = 0), the ALRMOUT pin reflects the status of the CKIN4

input. The equations below assume that the output alarm is active high; however, the active polarity is selectable

via the CK_BAD_POL bit.

Operation of the C1B, C2B, C3B, and ALRMOUT pins is enabled based on setting the C1B_PIN, C2B_PIN,

C3B_PIN, and ALRMOUT_PIN register bits. Otherwise, the pin will tri-state. Also, if INT_PIN = 1, the interrupt

functionality will override the appearance of ALRMOUT at the output even if ALRMOUT_PIN =1.

Once an LOS or FOS alarm is asserted for one of the input clocks, it is held high until the input clock is validated

over a designated time period. The validation time is programmable via the VALTIME[1:0] register bits as shown in

Table 48 on page 96. If another error condition on the same input clock is detected during the validation time then

the alarm remains asserted and the validation time starts over.

Note that hitless

switching betwee

n input clocks applies only when the input clock validation time

VALTIME[1:0] = 01 or higher.

For details, see "Appendix D—Alarm Structure" on page 144.

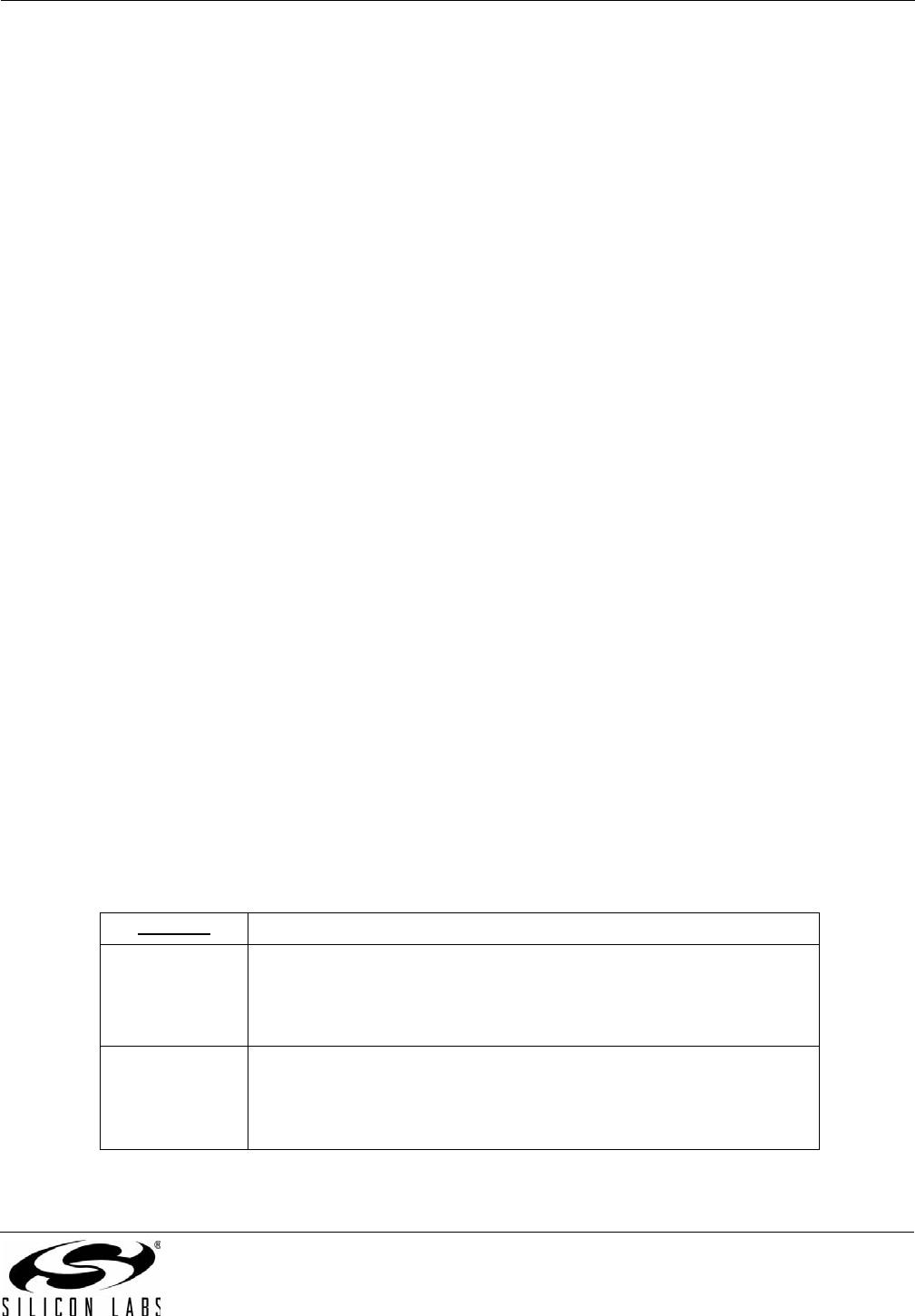

Table 52. Alarm Output Logic Equations (Si5367, Si5368, and Si5369 [CONFIG_REG = 0])

FOS_EN Alarm Output Equations

0

(Disables FOS)

C1B = LOS1_INT

C2B = LOS2_INT

C3B = LOS3_INT

ALRMOUT = LOS4_INT

1C1B = LOS1_INT or FOS1_INT

C2B = LOS2_INT or FOS2_INT

C3B = LOS3_INT or FOS3_INT

ALRMOUT = LOS4_INT or FOS4_INT