4-Port USB 2.0 Controller

Datasheet

SMSC USB20H04 Page 9 Revision 1.63 (03-30-07)

DATASHEET

Chapter 4 Interface Signal Definition

4.1 Pin Descriptions

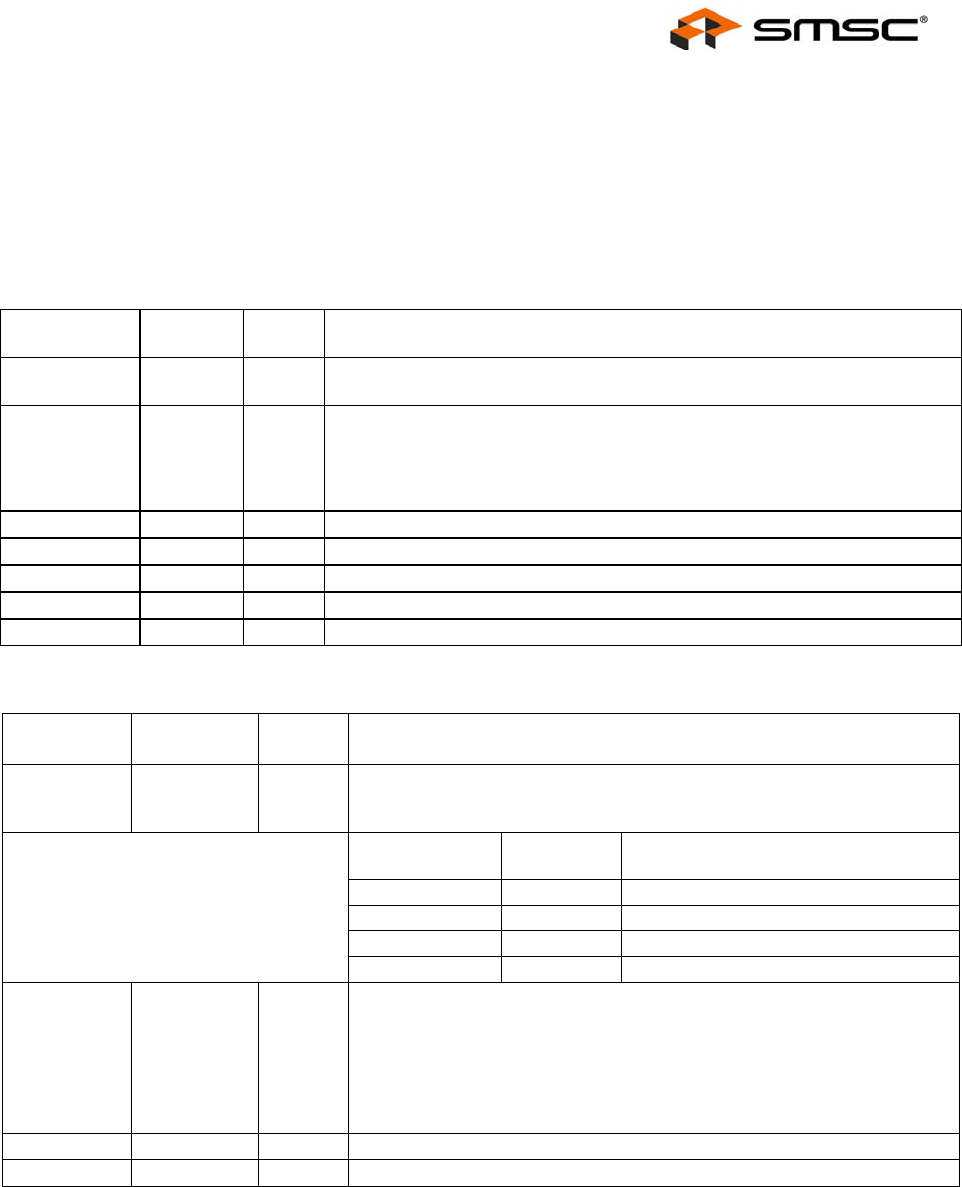

Table 4.1 - System Interface Signals

NAME

BUFFER

TYPE

ACTIVE

LEVEL

DESCRIPTION

RESET_N IS Low

Chip Reset. The minimum active low pulse is 100ns. See section 8.4 for a

complete description of operation following a reset.

SELF_PWR I High

Self-power Detect. Detects availability of local self-power source:

0: Self/local power source is NOT available (i.e., 4- Port Hub gets all power

from Upstream USB V

BUS

).

1: Self/local power source is available.

TEST_P0 IPD N/A

Test Pin. Do Not Connect

TEST_P1 IPD N/A

Test Pin. Do Not Connect

TEST_P2 IPD N/A

Test Pin. Do Not Connect

TEST_P3 IPD N/A

Test Pin. Do Not Connect

ATEST AO N/A

Test Pin. Do Not Connect

Table 4.2 – Configuration Select and Serial Port Interface

NAME

BUFFER

TYPE

ACTIVE

LEVEL

DESCRIPTION

SMB_SEL_N I N/A

SMBus Select. Selects between configuration via the SMBus interface, or

from an external EEPROM or using the internal default, as described in

the table below.

SMB_SEL_N CS/EE_SEL SMBus or EEPROM interface

configuration.

0 0 SMBus slave. Address: 0101100

0 1 SMBus slave. Address: 0101101

1 0 Internal default configuration.

1 1 2-wire EEPROM interface.

CS/EE_SEL IO8 N/A

Chip Select. This multifunction pin is sampled on the rising edge of

RESET_N. If SMB_SEL_N = 1, the internal default configuration will be

used when this pin is low, or the external I2C EEPROM will supply the

configuration when this pin is high. When SMB_SEL_N = 0, this pin

selects the SMBus slave address, as described in the table above.

Connect a 1k ohm resistor in series with the input when connecting this

pin to either VDD or VSS.

SD/SDA IOSD12 N/A

Serial Data. Data I/O on the 2-Wire interface.

SCK/SCL IOSD12 N/A

Serial Clock. Clock for the 2-Wire interface.