USB MultiSwitch

TM

Hub

Datasheet

SMSC USB2524 15 Revision 1.91 (08-22-07)

DATASHEET

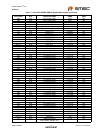

1 0 0 Internal Default Configuration

PRT_ASSIGN[3:0] = Peripheral Mode (Edge Triggered)

LED Mode = Host Ownership Mode

Strap

options on pins LED_A[4:1]_N are enabled.

Supports unassigned Ports

1 0 1 Internal Default Configuration

PRT_ASSIGN[3:0] = Peripheral Mode (Edge Triggered)

LED Mode = Host Ownership & Port Speed Mode

Strap options on pins LED_A[4:1]_N are disabled

Supports unassigned Ports.

110Reserved

111Reserved

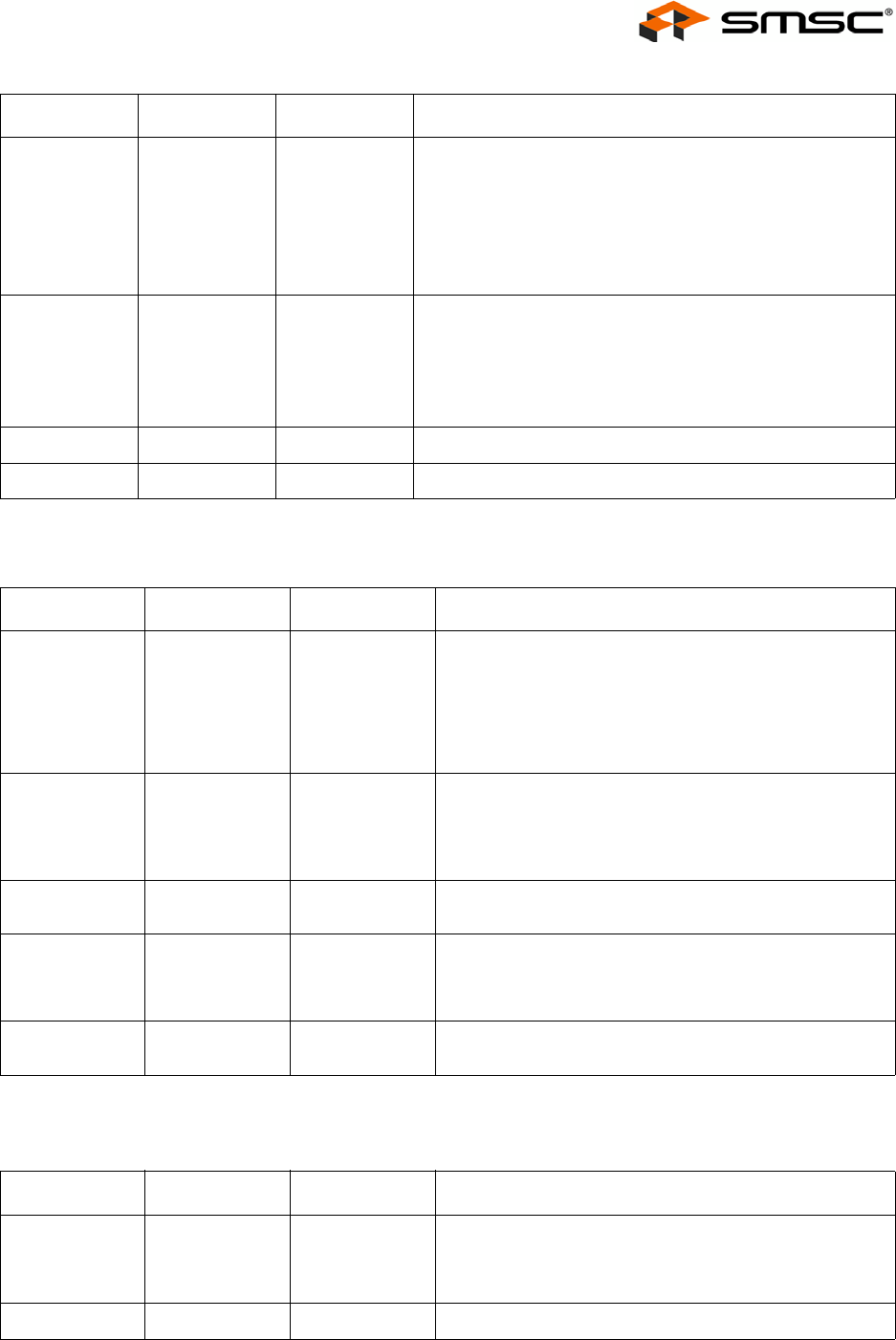

Table 4.3 Miscellaneous Pins

NAME SYMBOL TYPE FUNCTION

Crystal

Input/External

Clock Input

XTAL1/

CLKIN

ICLKx

24MHz crystal or external clock input.

This pin connects to either one terminal of the crystal or

to an external 24MHz clock when a crystal is not used.

Note: See Table 11.1 for the required logic voltage

levels of this pad if it will be driven by an

external clock source.

Crystal Output XTAL2 OCLKx

24MHz Crystal

This is the other terminal of the crystal, or left

unconnected when an external clock source is used to

drive XTAL1/CLKIN. It must not be used to drive any

external circuitry other than the crystal circuit.

RESET Input RESET_N IS This active low signal is used by the system to reset the

chip. The minimum active low pulse is 1us.

Self-Power /

Bus-Power

Detect

SELF_PWR I Detects availability of local self-power source.

Low = Self/local power source is NOT available (i.e., Hub

gets all power from Upstream USB VBus).

High = Self/local power source is available.

TEST Pin TEST IPD Used for testing the chip. User must treat as a no-

connect or connect to ground.

Table 4.4 Power, Ground, and No Connect

NAME SYMBOL TYPE FUNCTION

VDD Core VDDCR18 +1.8V core power.

Pins 16 and 50 must have a 4.7μF (or greater) ±20%

(ESR <0.1Ω) capacitor to VSS

VDDIO 3.3V VDD33 +3.3V Power Supply for the Digital I/O.

Table 4.2 SMBus or EEPROM Interface Behavior (continued)

NAME NAME NAME FUNCTION