High Speed Inter-Chip USB 2.0 Hub and Flash Media Controller

Datasheet

SMSC USB4640/USB4640i 15 Revision 1.0 (06-01-09)

DATASHEET

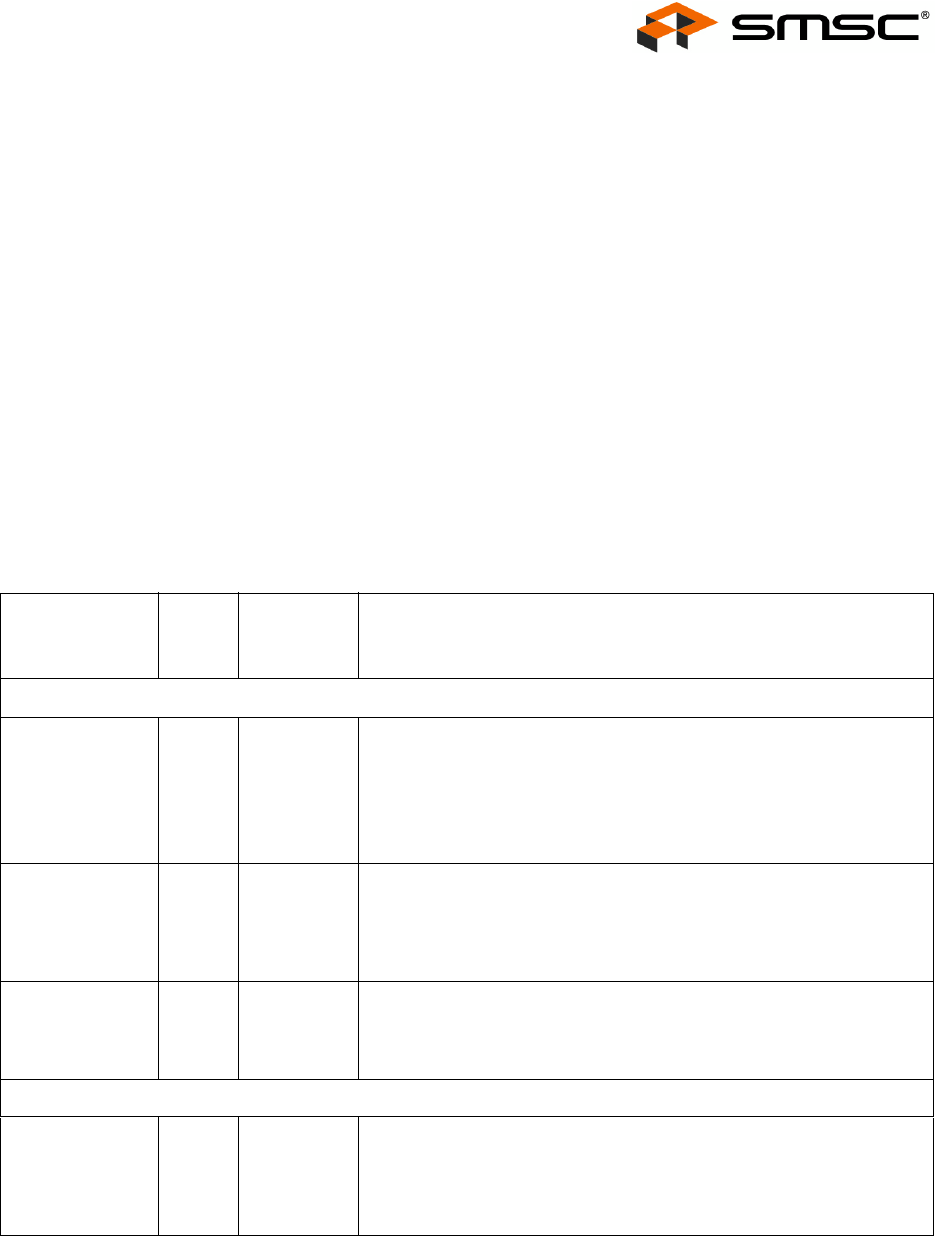

Chapter 6 Pin Descriptions

This section provides a detailed description of each signal. The signals are arranged in functional

groups according to their associated interface. The pin descriptions below are applied when using the

internal default firmware and can be referenced in Chapter 8, "Configuration Options," on page 28.

Please reference Chapter 2, "Acronyms," on page 10 for a list of the acronyms used.

The “n” symbol in the signal name indicates that the active, or asserted, state occurs when the signal

is at a low voltage level. When “n” is not present in the signal name, the signal is asserted at a high

voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working

with a mixture of “active low” and “active high” signals. The term assert, or assertion, indicates that a

signal is active, independent of whether that level is represented by a high or low voltage. The term

negate, or negation, indicates that a signal is inactive.

6.1 USB4640/USB4640i Pin Descriptions

Table 6.1 USB4640/USB4640i Pin Descriptions

SYMBOL

48-PIN

QFN

BUFFER

TYPE

(Table 6.2)DESCRIPTION

UPSTREAM HSIC INTERFACE

HSIC_IMP 39 I HSIC Impedance Control

This pin selects the driver impedance of the HSIC_DAT and

HSIC_STROBE pins.

‘1’ = approximately 50

Ω impedance

‘0’ = approximately 40 Ω impedance

HSIC_DAT 42 I/O HSIC Data

This is the bi-directional double data rate (DDR) data signal that is

synchronous to the HSIC_STROBE signal as defined in the High-

Speed Inter-Chip USB Specification, Version 1.0.

HSIC_STROBE 43 I/O HSIC Strobe

This pin is the bi-directional data strobe signal that is defined in the

High-Speed Inter-Chip USB Specification, Version 1.0.

DOWNSTREAM USB INTERFACE

USBDN_DM

[3:2]

USBDN_DP

[3:2]

3

1

4

2

I/O-U USB Bus Data

These pins connect to the downstream USB bus data signals and

can be swapped using the PortSwap feature (See Section 8.4.4.20,

"F1h: Port Swap," on page 47).