12

S93WD462/S93WD463

2029 2.2 1/23/01

SUMMIT MICROELECTRONICS, Inc.

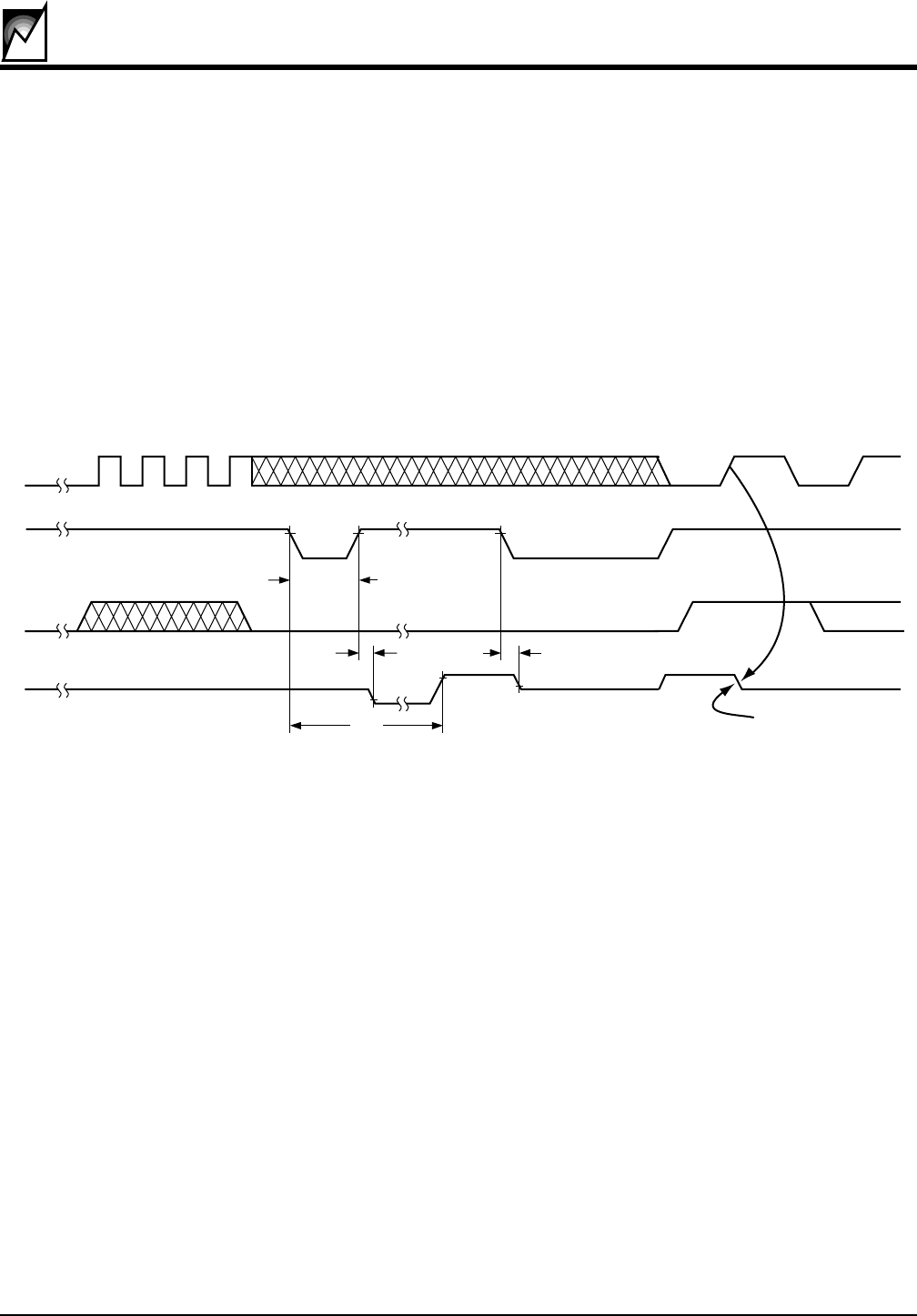

Ready/Busy Status

During the internal write operation the S93WD462/WD463 memory array is inaccessible. After starting the write

operation (taking CS low) the host can implement a 10ms timeout routine or alternatively it can employ a polling routine

that tests the state of the DO pin.

After starting the write, testing for the status is easily accomplished by taking CS high and testing the state of DO. If

it is low the device is still busy with the internal write. If it is high the write operation has completed.

For the polling routine the host has the option of toggling CS for each test of DO, or it can place CS high and then

intermittently test DO. SK is not required for any of these operations. Once the device is ready, it will continue to drive

DO high whenever the S93WD462/WD463 is selected. The ready state of DO can be cleared by clocking in a start

bit; this start bit can either be the beginning of a new command sequence or it can be a dummy start bit with CS returning

low before the host issues a new command.

SK

2029 ILL 13.0

CS

DI

DO

t

CS

HIGH-Z

HIGH-Z

STATUS CLEARED

BUSY READY

STATUS VERIFY

t

SV

t

HZ

t

EW